基于电荷耦合器件的雷达视频积累电路

摘要:电荷耦合器件是一种发展前景良好的金属氧化物半导体(MOS)集成电路。该电路广泛应用于彩色成像、信号处理等相关领域。文介绍一种用CCD32l型电荷藕合器件设计和实现的脉冲雷达视频积累电路,目的在于探讨使用该器件实现雷达视频积累的可行性和实际效果。实践证明,使用该器件实现雷达信号积累能有效地提高雷达的信噪比,改善雷达的检测能力,达到增加雷达的发现概率和探测距离的目的。经测试,使用该电路可使雷达信噪比可提高3.5dB。

关键词:电荷耦合器件;信噪功率比;视频积累;传递函数

O 引言

对于早期脉冲雷达的信号积累主要依靠显示器余辉特性及雷达操纵员眼和脑的储存能力来完成。由于这种积累加入了许多人为因素,对显示器的余辉性能也提出了严格要求,而且积累效果也是因人而异。因此、近年来,随着大规模集成电路和高速微处理器的发展,在改造老雷达,充分发挥老雷达性能方面人们提出了许多可行的技术方案。雷达信号积累能有效地提高雷达的信噪比,改善雷达的检测能力,达到增加雷达发现概率和探测距离的目的。雷达信号积累分为相干积累和非相干积累。相干积累是指雷达的发射和接收载频有确定的相位关系,积累在中频实现。非相干积累是指雷达的发射和接收载频无确定的相位关系,积累在检波后实现。早期的雷达大部分属于非相干雷达,因此,对这类雷达进行信号积累应在检波后,属于视频积累。视频积累较中频积累简单易行,在手段上可采用微处理器及软件编程,也可以用电荷耦合器件及其电路来实现。本文介绍的用电荷耦合器件实现的视频积累电路成本低廉,适合在中高档雷达或改造老雷达上使用。

![]() 是噪声功率提高了N倍。则积累后输出电压的信噪比为

是噪声功率提高了N倍。则积累后输出电压的信噪比为![]() 因此电压信噪比改善为:

因此电压信噪比改善为:![]() 信噪功率比提高了N倍。

信噪功率比提高了N倍。

2 设计方案

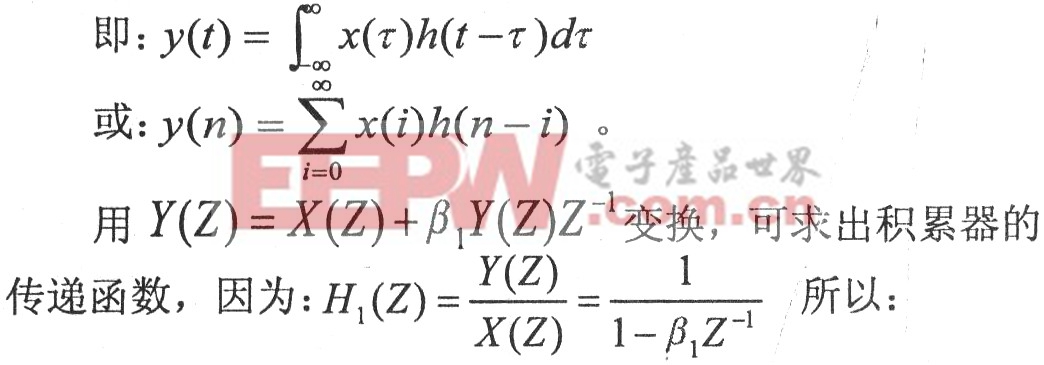

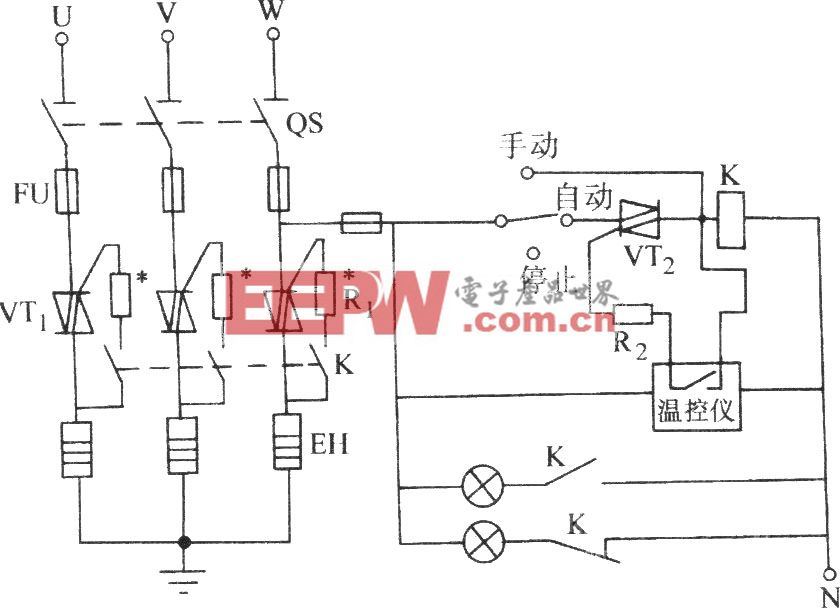

要实现雷达信号累积相加,一种简单的方案是把雷达的回波信号延迟一个雷达发射脉冲周期,与未经延迟的回波信号依次相加,实现信号的积累。本方案采用的是一次递归型视频积累电路,原理如图1所示。由于延迟线是线性网络,所以通过线性网络的输出y(t)是输入x(t)和网络脉冲响应h(t)的卷积,

(βl为反馈网络增益,应小于1)

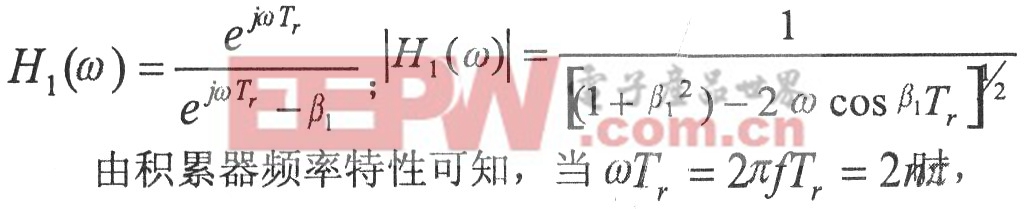

由传递函数可知,积累器是单极点系统,它在Z平面β1处有一极点,如图2所示。由于Z=esTr,用S=jω代入传递函数得出积累器的频率特性;

|H1(ω)|为最大值:当ωTr=(2n+1)π时,|H1(ω)|最小。频率特性如图3所示。因此,积累器实际上是一个线性梳状滤波器。

3 CCD321型电荷耦合器件性能介绍

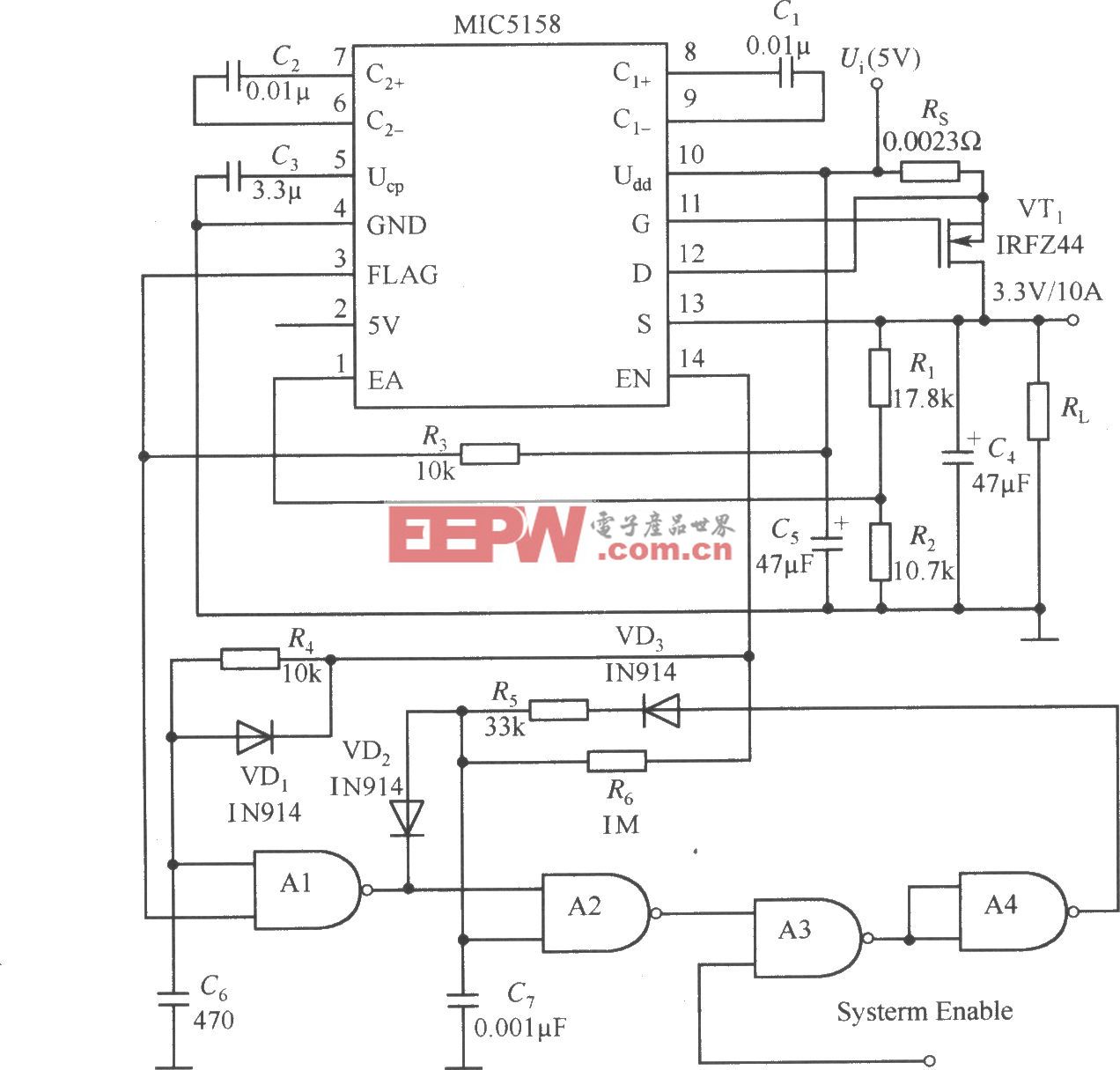

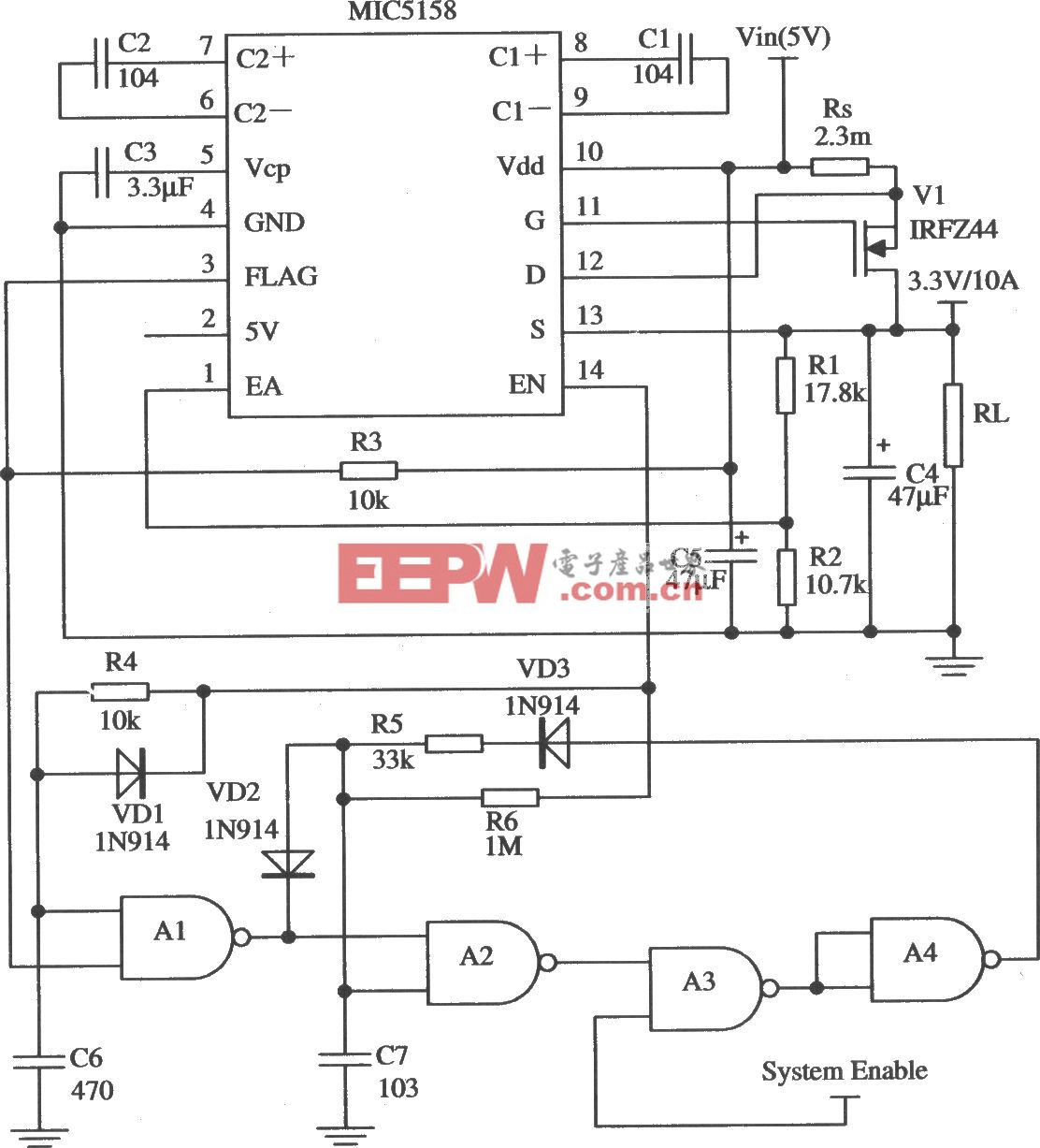

电荷藕荷器件CCD321是一种电予可变模拟延迟线,可完成电信号的延迟和暂存模拟信息,时间相关和增强信噪比。它由2个455位的移位寄存器A和B组成,根据需要,每个移位寄存器可单独使用,也可串联使用构成910位移位寄存器。每个移位寄存器都有自己的信号注入端、信号输出端以及时钟和采样脉冲输入端。该器件由单相时钟驱动,由采样脉冲采集信号的输入与输出,因此,输出信号在时间上是离散的,在幅度上是模拟的,具有数字信号与模拟信号的特点。该器件信号带宽5MHZ,增益3―6dB,信噪比55―60dB,是用于采样及信号处理的理想器件。它的引脚功能见表1,定时图如图4所示,电路图如图5所示。

4 视频积累电路设计

图6是用CCD321设计的视频积累器电路原理图。CCD32l的两个移位寄存器A和B串联使用构成910位移位寄存器。视频信号经910位移位寄存器后应延时一个雷达发射脉冲周期Tr。因此,移位时钟和采样脉冲频率为![]() 在雷达发射脉冲频率300Hz,发射脉冲宽度lOμs条件下,加在电荷耦合器件上的移位时钟和采样脉冲频率为,f=910×300=273KH在发射脉冲宽度内采样次数n=10×10-6×273×l03=273因此,在这个采样频率下采样存储信号满足奈奎斯特采样定理。图中所示,由ICIA、ICIB、ICIC、IC2A、IC2B及石英晶体等组成转移时钟和采样脉冲产生电路,TNI21为采样脉冲整形电路。视频检波信号经电压跟随器IC3A加到采样保持电路。采样保持电路由IC5及保持电容C1组成。采样保持电路对输入的视频信号进行采样,使直通信号与被延时信号幅频特性一致。经IC5采样后的信号送到加法器IC3B的一个输入端。加法器的输出分为两路:一路送入CCD32l输入端(3脚)进行延时,经910位延时后,从第15脚输出,再经W1和R6分压后送入电压跟随器IC4A。电压跟随器的输出将信号反馈到加法器的另一个输入端,实现延时信号与未延时信号的相加。其中、W1和R6是确保反馈系数β1小于1而设置的。加法器的另一路输出送到电压跟随器IC4B。该电压跟随器起隔离作用,其输出即为视频积累信号。

在雷达发射脉冲频率300Hz,发射脉冲宽度lOμs条件下,加在电荷耦合器件上的移位时钟和采样脉冲频率为,f=910×300=273KH在发射脉冲宽度内采样次数n=10×10-6×273×l03=273因此,在这个采样频率下采样存储信号满足奈奎斯特采样定理。图中所示,由ICIA、ICIB、ICIC、IC2A、IC2B及石英晶体等组成转移时钟和采样脉冲产生电路,TNI21为采样脉冲整形电路。视频检波信号经电压跟随器IC3A加到采样保持电路。采样保持电路由IC5及保持电容C1组成。采样保持电路对输入的视频信号进行采样,使直通信号与被延时信号幅频特性一致。经IC5采样后的信号送到加法器IC3B的一个输入端。加法器的输出分为两路:一路送入CCD32l输入端(3脚)进行延时,经910位延时后,从第15脚输出,再经W1和R6分压后送入电压跟随器IC4A。电压跟随器的输出将信号反馈到加法器的另一个输入端,实现延时信号与未延时信号的相加。其中、W1和R6是确保反馈系数β1小于1而设置的。加法器的另一路输出送到电压跟随器IC4B。该电压跟随器起隔离作用,其输出即为视频积累信号。

5 实验中注意的问题

(1)定做一只振荡频率f0=273KHz的石英晶体,且频率稳定度要高。CCD32l第4脚、第12脚、第14脚的直流电压要正确。Vcc采用+12V电源供电,转移时钟及采样脉冲为TTL电平、波形要规整、否则采样时漏电流较大、采样“漏钟”干扰不移消除。

(2)从雷达视频检波器输出、视放输入端断开电路,然后分别接入图6所示的电路,输入信号要确保小于1VP―P。

(3)电源电路要加去藕措施,纹波要小。数字地与模拟地要分开设置,否则容易引起相互串扰。

6 结束语

用CCD321设计的雷达视频积累电路可以提高雷达的信噪比,改善雷达的检测能力和增加探测距离。经测试,视频检波输出信号为0.4V,噪声为0.3V,信噪比为Si/Ni≈1.33。经视频积累电路后,输出视频信号为lV,噪声为0.5V,信噪比为Soi/NoN≈2。因此信噪比提高了20(1g2一lgl.33)≈3.5db。

评论