一款雷达芯片的基于扫描路径法可测性设计

基于扫描路径法的可测性设计技术是可测性设计(DFT)技术的一个重要的方法,这种方法能够从芯片外部设定电路中各个触发器的状态,并通过简单的扫描链的设计,扫描观测触发器是否工作在正常状态,以此来检测电路的正确性。但随着数字电路朝着超大规模的方向发展,设计电路中使用的触发器的数目也日趋庞大,怎样采用合适的可测性设计策略,检测到更多的触发器,成为基于扫描路径法的一个关键问题。

本文采用基于扫描路径法的可测性设计技术,对一款约750万门级雷达芯片的实际电路进行可测性设计。在设计中通过使用时钟复用技术、时钟电路处理技术以及IP隔离技术等几种有效的设计策略,大大提高了芯片的故障覆盖率,最终达到可测性设计的目的。

1 扫描链设计原理

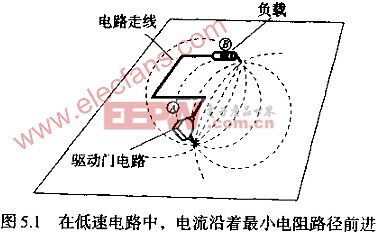

数字电路由大量的组合元件和时序元件组成,时序元件具体体现为单个的触发器(DFF)。数字电路基本组成如图1所示。其中系统时钟(CP)来控制各个触发器的数据端口相应数据的输入输出。

基于扫描路径法的可测性设计就是将电路中的时序元件触发器替换为相应的可扫描的时序元件扫描触发器(SDFF);然后将上一级扫描触发器的输出端(Q)连接到下一级的数据输入端(SDI),从而形成一个从输入到输出的测试串行移位寄存器,即扫描链(ScanChain);通过CP端时钟的控制,实现对时序元件和组合逻辑的测试。实现扫描链设计后的电路如图2所示。

采用扫描设计技术后,在扫描控制端(SEN)和时钟端的控制下,通过扫描数据输入端,可以把需要的数据串行地移位到扫描寄存器单元中,串行地控制各个单元;同时也可以通过扫描输出端(Scan_out)串行地观测它们。这样就增加了时序电路的可控制性和可观测性。

2 扫描链策略设计

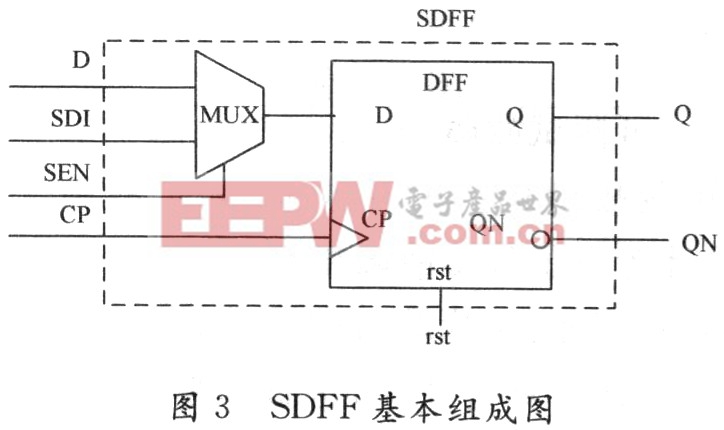

图2中虚线部分为扫描触发器,即扫描链的基本组成单元,其构成原理如图3所示。

扫描链设计前,电路中的触发器都是通过系统时钟端口控制数据的变化,因而在做扫描设计时可以通过系统时钟复用检测到更多的触发器,以此达到控制扫描触发器的目的。

同样的道理,一些特殊电路中的触发器也是采用手动或者软件的方法将它们串联到扫描链中,以此增加可扫描的触发器数,最终使故障覆盖率得以提高。但需要注意的是,这些可测性设计策略应用的前提是不能改变原始设计的功能。

3 设计中采用的策略

在进行DFT设计并插入扫描链的时候,最为重要的一个问题就是测试覆盖率,而它的最终值是由触发器的总数和最终能够测试到的触发器的数目的比值决定的,因此是否能够尽可能多地测试到本雷达芯片电路中的触发器,成为扫描路径法设计的一个关键问题。针对实际的设计电路提出了以下三种有效的设计策略,由最终测试结果可知,采用此设计策略后可大大提高测试覆盖率,满足设计指标需要。

3.1 时钟复用技术

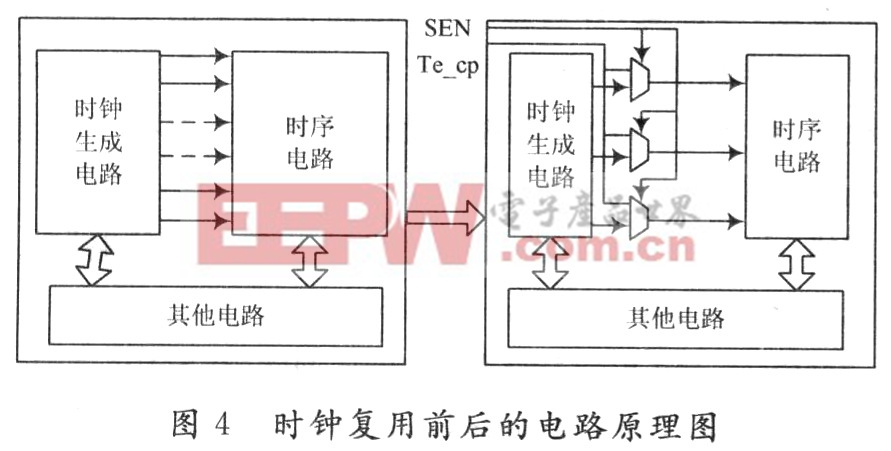

每个触发器都受系统时钟控制,系统时钟能够覆盖本设计中大部分的触发器元件,因而考虑使用时钟复用技术,在插入扫描链进行测试时,把测试时钟引入到系统时钟上,这样测试时钟就能覆盖尽可能多的触发器,并在插入扫描链后,替换成扫描触发器。其实现原理如图4所示。

从图中可以看出,时钟电路产生很多不同频率的时钟以满足不同模块的需求,在时钟电路的输出端口加入相应的选择器(MUX)控制时钟的选择;当处于正常工作状态时,MUX选择正常的时钟进入相应的模块,进而实现相应的功能;当处于扫描状态时,这些MUX都是选择同样的扫描测试时钟信号(Te cp)进人到各个模块进行测试。这样做的优点在于不仅满足了测试选择的需要,而且也尽可能地测试到所有触发器,满足测试覆盖率的需要。

3.2 特殊时钟电路处理

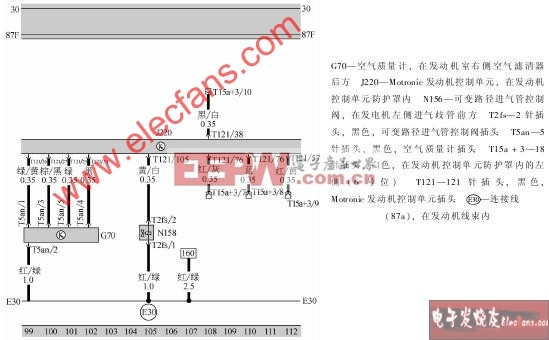

在本设计中存在很多特殊的电路,其中有一种时钟发生电路是不能进行扫描路径法的可测性设计,具体的电路图如图5所示。

在这种结构中,时钟从第二个触发器的Q端输出,输入到第三个触发器的时钟(CP)端。由于扫描时钟无法控制第三个以及后续的触发器,设计的扫描链将不会覆盖之后的电路,结果导致故障覆盖率降低,测试覆盖率也会下降。

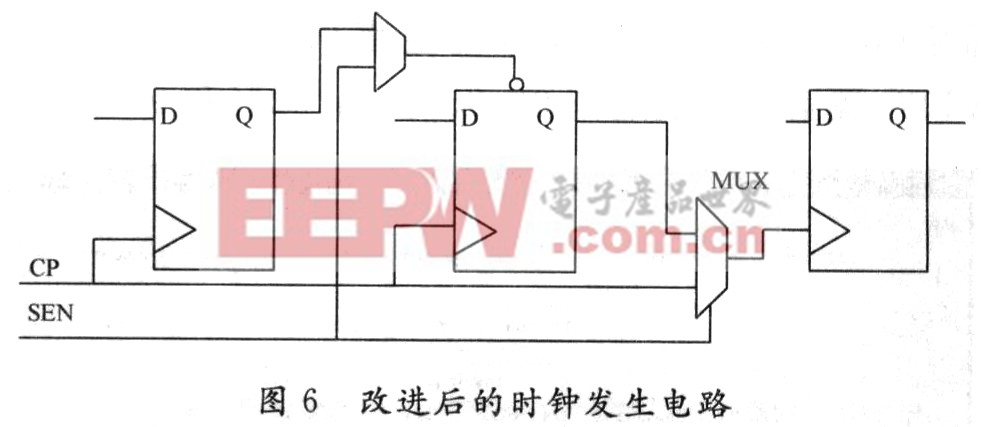

改进此种电路结构的方法是手动或者用软件方式增加一个MUX选择器,当在扫描链插入时,正常的控制时钟信号就会进入第三个触发器的时钟端。具体实现的电路结构如图6所示。

使用此策略,在插入扫描链后,当MUX选择器处在扫描状态时,扫描时钟就会连接到后续的触发器,并将其连接到扫描链上,这样就会大大提高故障覆盖率,从而提高测试覆盖率。

评论