基于PCIe总线的超高速信号采集卡的设计

摘要:设计一种基于PCIe总线的不间断采样和传输的超高速数据采集卡。利用双400MHz、14位AID转换器实现了800 MHz、14位的信号高速、高精度采集,论述了利用Xilinx公司FPGA的IPCORE设计实现PCIe总线控制接口。基于PCIe总线,采用乒乓交换数据传输的机制,实现了高速采样数据流的不间断传输。最后给出了实际采集数据的频谱。利用该采集卡构成的数据采集系统在雷达侦察和干扰领域拥有很高的实用价值和广阔的应用前景。

关键词:数据采集;PCIe;FPGA;雷达对抗

在雷达对抗系统中,需要对于雷达信号进行实时测频,并可以对感兴趣的信号进行储频,为假目标欺骗干扰或压制干扰提供测频结果和储频数据。而数字测频是当今发展最快的测频技术之一。数字测频、储频的关键技术之一即是超高速、高精度、不间断的信号采集技术。采样速率和精度的不断提高,使得数据传输和存储越来越成为数据采集系统的技术瓶颈。目前大部分高性能数据采集卡都是基于PCI、CPCI、VME等总线,最高持续传输速率难以超过400 MB/s,因此大多数采集卡采用采集和存储分时工作的模式,即在板内设有一定容量的存储器,当存储器存储数据到一定量时,停止采集而开始上传数据,上传完毕后再重新启动采集,不断循环,文献也提出采集传输的流水工作模式,提高采集的效率。这些工作方式虽然也能满足大部分数据采集的要求,但是在信号非常密集的环境中,交替工作模式将导致侦察截获概率降低,带来干扰的效能下降。基于上述原因,本文论述了一种基于PCIe总线的数据采集卡,该采集卡不但可以达到800 MHz/s采样率、14 bit采样精度,还具有不间断采集、实时上传的能力(在测频只取其中8位分辨力,储频时取14位分辨力,根据系统的总数据量可编程)。该采集卡可以与高速信号处理器配合使用,构成信道化的数字测频、储频系统,双信道系统的组成示意图见图l。

1 系统总体设计

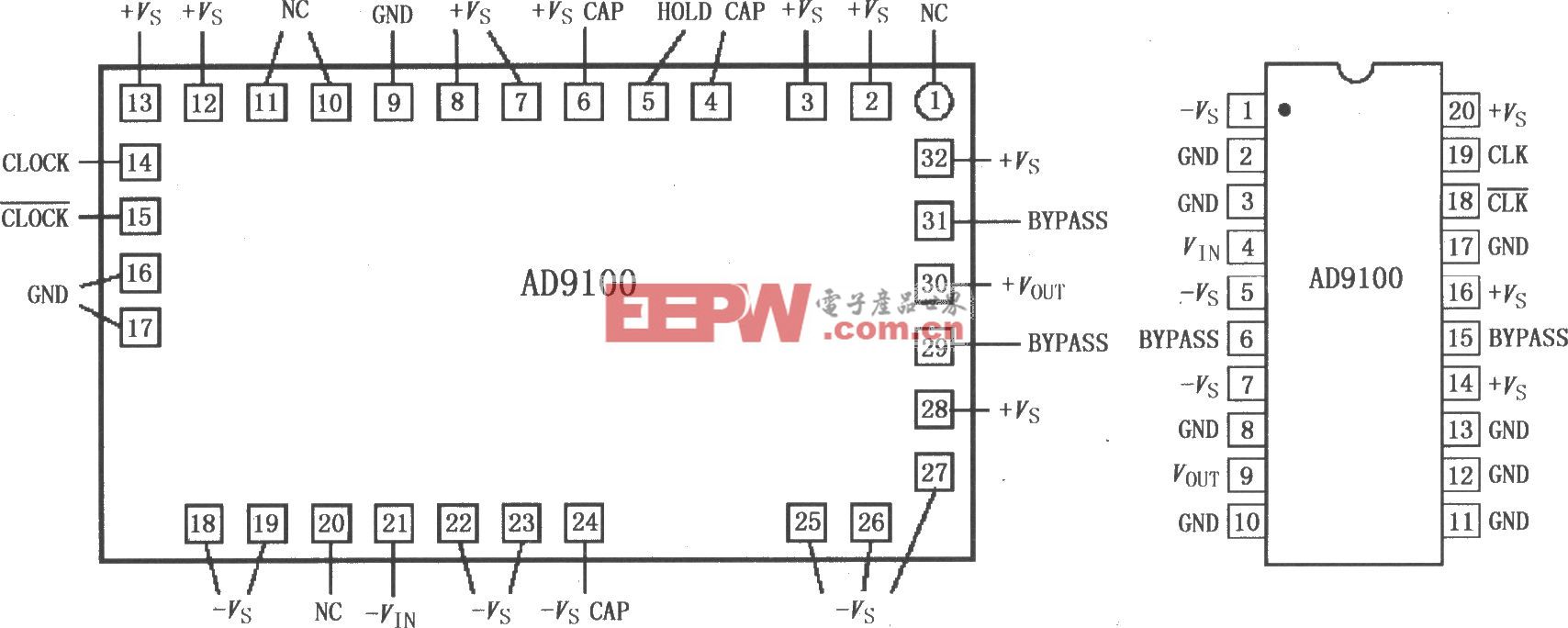

本采集卡的设计主要包括超高速A/D转换器模块、时钟产生模块、大容量存储器模块和基于FPGA的控制模块。如图2所示,待采集的模拟信号经过信号调理放大到合适的电平范围,送入到两片工作于交叉采样模式的A/D转换器,转化后数字信号直接送至FPGA控制器,在FPGA内部实现信号电平转换数据缓冲后,首先存储于A路动态存储器中,当A路存储器存满后,数据立即转存于B路存储器,同时启动数据上传操作,将A路存储器的数据通过DMA方式上传至主机存储或传输到信号处理板中;当B路存储器存满后,数据存储立即切换至A路存储器,同时也启动B路存储器的上传操作,如此反复循环。由于PCIe接口传输速率大于信号采集速率,因此可以保证数据的不丢失。

评论