基于SOPC的自定义外设FIFO

摘要:以Altera公司的FPGA芯片EP2C20Q208C8为例,详细介绍了在QuartusII 7.2的环境下,用SOPC Builder构建Nios软核时,自定义FIFO接口元件的方法。通过将采集到的电压信号,在数码管上显示的实验,实现FIFO寄存器与Nios CPU之间的通信。

关键词:现场可编程门阵列FPGA;Nios;先进先出;可编程片上系统Builder

0 引言

随着微电子技术和半导体工业的不断发展,数字技术已进入片上系统时代。从而又发展了SOPC(可编程片上系统),SOPC是Altera 公司提供的片上可编程系统解决方案。Nios嵌入式处理器是Altera公司推出的软核CPU,提供给用户,并在Altera的FPGA上实现优化,用于 SOPC集成

并在FPGA上实现,提高了系统的灵活性和扩大范围。

自定义外设是SOPC系统灵活性的重要体现,是SOPC系统中极其重要的一种设计方法。在大量的数据常需要处理时,利用自定义外设由具体的硬件来实现,可以极大程度地提高系统运行的速度,同时便于系统的模块化与集成化,是SOPC系统设计的重中之重。定制的用户外设能够以“硬件加速器”的形式实现各种各样用户要求的功能。

1 定制Avalon总线型FIFO接口元件

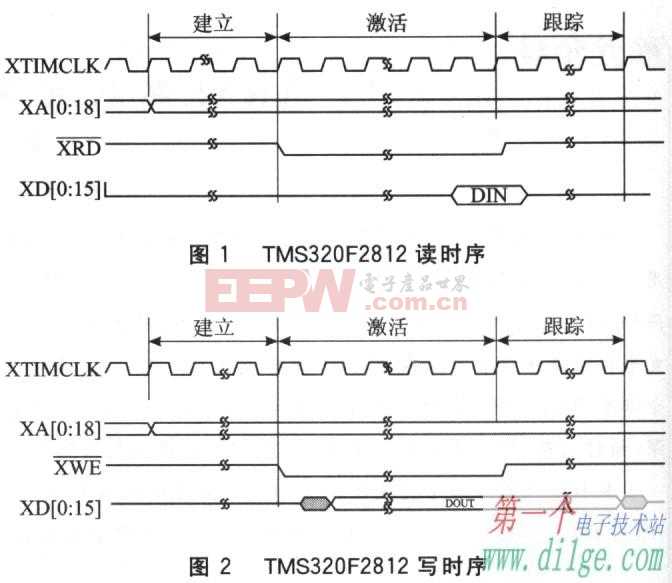

由于选用的AD采样速率非常高,并且只由时钟控制端控制,因此设计时在AD采集模块和Nios CPU之间加一个FIFO存储器,从系统外部接口送来的数据先在FIFO中缓存,然后将数据读入SDRAM,在片上进行数据处理。整个流程在FPGA平台上采用SOPC方法实现。在SOPC Builder中只有厂商提供的片上FIFO接口控制器,没有外部使用的FIFO接口控制器核,因此需要用户自定义FIFO接口控制器,这样才能满足系统外围电路的应用要求。文中采用创建元件配置向导定制FIFO接口元件的方法。

2 用户自定义IP核的开发流程

自定义外设作为NiosII软核处理器超强灵活性的体现,它的开发要遵循一定的规律。一个用户自定义外设必须用硬件描述语言来描述硬件的逻辑。用户自定义IP按照对Avalon总线操作的不同可分为Avalon Master、Avalon Slaver和Avalon Streaming外设。由于Avalon Master和Avalon Streaming外设的开发比Avalon Slave外设要复杂,所以用户开发的外设大部分为Avalon Slave外设,但是开发流程是一样的。典型的Avalon外设的开发步骤如下:

(1)规划元件的硬件功能。若采用微控制器控制该元件,则规划访问该硬件的应用程序接口(API);

(2)在硬件和软件要求的基础上,定义一个恰当的接口(一般为Avalon Slave端口);

(3)使用硬件描述语言描述硬件逻辑。一个典型元件的硬件架构一般由接口模块、寄存器文件模块和行为模块3部分组成。接口模块作为顶层模块,定义总线接口信号;寄存器文件模块完成该元件与外部信号的通信,提供访问与控制元件的逻辑界面;行为模块实现元件的硬件功能。片上总线Avalon从端口的信号都不是必须的,一个典型的Avalon从端口所包含的信号如表1所示。

(4)单独验证元件的硬件功能;

(5)写用于描述寄存器的C头文件为软件定义硬件寄存器映像;

(6)写元件的驱动软件;

(7)把通过测试的源代码使用元件编辑器封装硬件HDL和软件文件,完成元件定制。

3 自定义FIFO接口的开发

3.1 硬件构建

3.1.1 接口模块的设计

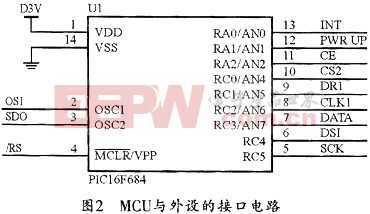

根据FIFO的功能需要,该模块所需的Avalon总线输入信号为clk、reset n、data、full、empty信号,而模块输出则为rdclk、rdreq、wrreq信号。该接口模块定义了总线接口信号,作为顶层模块。

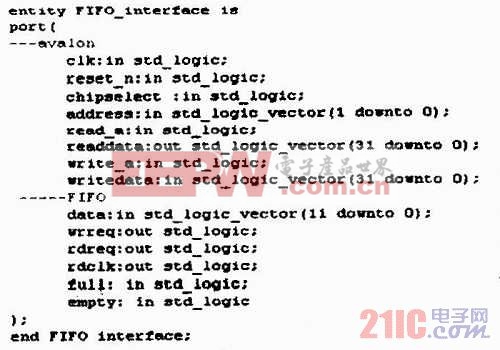

Avalon总线接口设计文件的端口说明部分如下:

3.1.2 寄存器文件模块

寄存器文件模块实现与外部信号的通信,提供了访问与控制元件界面。在寄存器文件中,Avalon总线的地址信号有两位,00表示读取数据寄存器,O1表示读取状态寄存器,10表示写控制寄存器,address的11保留。在片选和读信号的控制下,分别读数据寄存器和状态寄存器。在片选和写信号的控制下,向控制寄存器写入数据。

评论