一种多路图像采集系统的软件设计

4.3 LCD/VGA显示控制器

本模块主要是用FPGA来产生LCD/VGA显示时所需要的时钟信号CLK(像素时钟信号)、VSYNC(帧同步信号)、HSYNC(行同步信号)和使能信号(VDEN),并在相应控制时序的作用下,依次将显示缓存即SRAM中的数据依次读出,输出到LCD上的过程。

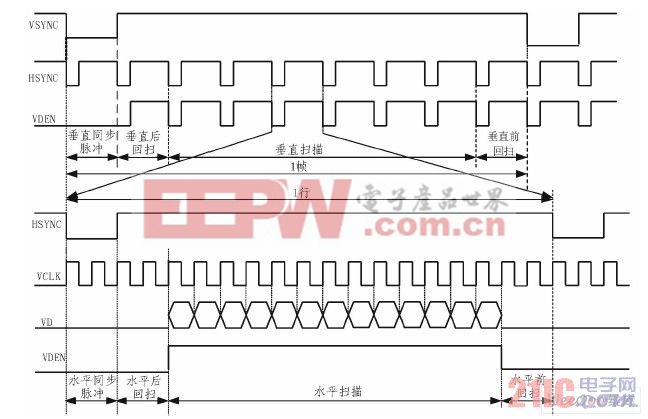

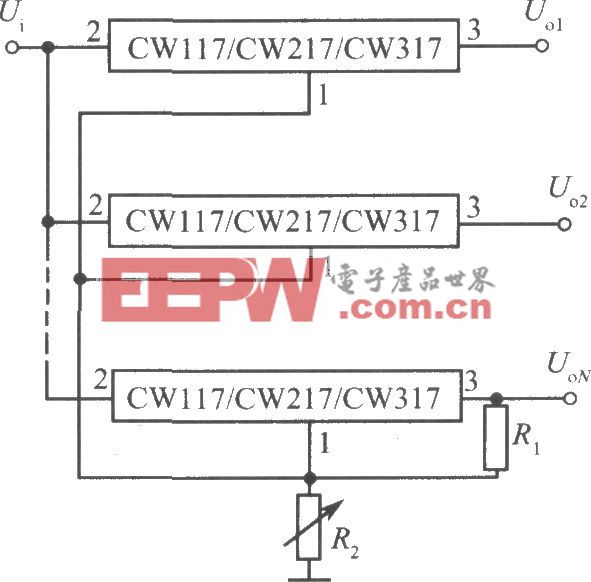

LCD显示所需的主要时序信号的关系如图7所示。

图7 LCD时序信号图

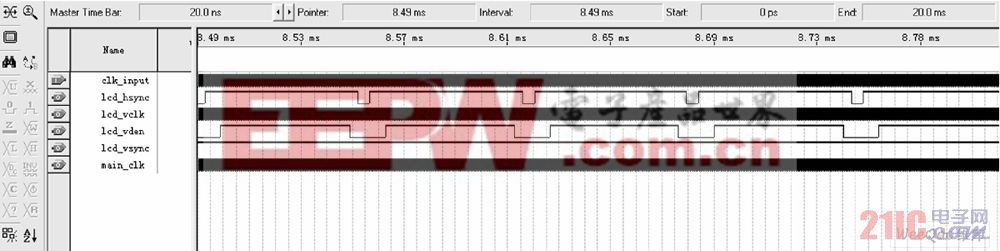

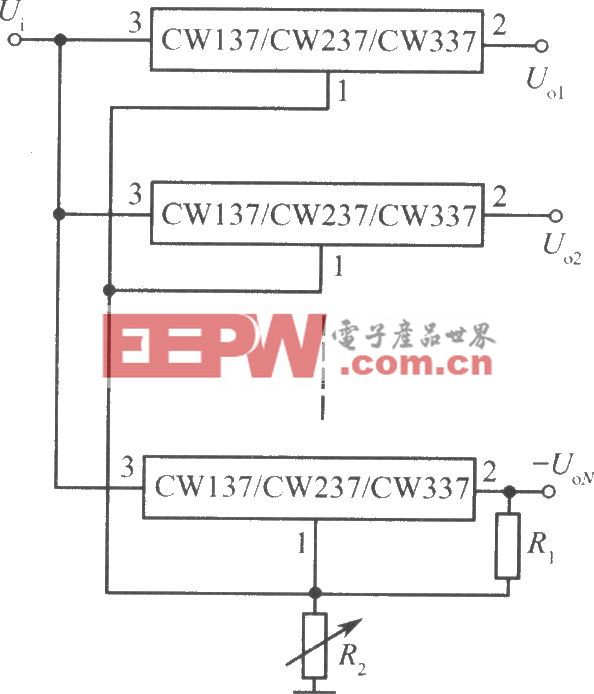

在系统中,LCD屏幕分辨率为640x480,像素时钟CLK为25MHz,由于FPGA的主时钟输入选用了20 MHz的有源时钟,那么就要求利用Cyclone芯片的内部逻辑资源来实现时钟倍频,以产生所需要的CLK(25 MHz)、用Verilog语言编写参数化的时序生成模块,产生HSYNC(32 kHz)及VHY-NC(60 Hz)时钟信号,如图8所示。

图8 时序验证

VGA显示原理与LCD相似,除了在硬件上正确连接ADV7125芯片电路外根据需要的分辨率来生成相应时钟信号即可。

5 图像抖动的分析与解决

在系统完成后软硬件联调时,出现画面抖动现象,其中以RTSO为基准而产生乒乓切换的那一路图像稳定,其他三路都出现不同程度的抖动现象。对此我们做了深入的分析和实验,分析整个系统的结构可知,系统在多个时钟控制下共同工作,也就是所说的典型的异步系统。我们知道,数据在异步系统传输时对时钟要求非常严格,稍微的一点时钟偏差都会带来对有效像素截取的偏差,最终影响图像的显示质量。

解决的办法有两个,一是加入缓冲机制,利用FIFO对数据存储的特性来实现数据在异步时钟之间的无缝传输;二是同步时钟,利用状态机等方法使得异步系统的时钟能够尽可能同步。采用第二种方法对系统进行改进,首先系统中所有的分频、倍频尽量使用Quartus 6.0自带的PLL

PLL

pll是锁相环(Phase-Locked Loop)的英文简称,用来使外部的输入信号与内部的振荡信号同步。pll是用于振荡器中的反馈控制电路。 [全文]

产生,并且使用专用时钟引脚进行时钟输出;其次把写时钟write_clk降为54M,也就是每隔一个像素采集一次。最终,四路图像都能稳定显示。

6 结束语

本文实现了一种结合Altera公司生产的CycloneII系列FPGA与视频解码芯片ADV7181B的嵌入式图像采集系统。系统具有低功耗、低成本、高可靠和灵活性好等特点。基于FPGA的多路图像采集系统采用两片FPGA作为主控芯片,完成四路视频画面的同时显示和切换,实现两个FPGA的级联配置,采用Verilog语言编写的控制逻辑解决了画面抖动问题。系统软件集成度高,硬件结构清晰简单,即可满足一般监控场合对多处位置进行实时监控的需求,又能为功能更复杂的图像处理、压缩、传输系统提供前端图像数据采集。

评论