基于ADV7183A视频采集系统的设计

摘要 利用FPGA控制视频解码芯片ADV7183A,从而输出8 bit的YCrCb型4:2:2的视频数据,再将其进行隔点采样,得到320×256的灰度图像数据,并传输给DSP,由DSP显示的采样数据达到设计要求,为后来的滤波处理提供良好的数字视频数据。

关键词 FPGA;ADV7183A;视频采集;YCrCb

人的感觉器官中接受信息最多的是眼睛。为了存储视觉信息,模拟视频信号必须通过模拟/数字(A/D)转换器转变为数字的“0”或“1”,这个转变过程就是所谓的视频捕捉。

在数字图像处理中,一般采用单片机控制芯片的I2C总线,而对数据的采集处理,则可以用专用的数字处理芯片DSP或FPGA进行。随着FPGA器件集成度的增长,完全有能力将ADV7183A的控制电路集成到FPGA内部完成。这样实现了设计的小型化、低功耗,并利用FPGA现场可编程特征充分发挥了ADV7183A的功能。

传统上是利用I2C总线控制HS,VS和FIELD,并根据这3个信号的有效电平采集有效视频,然而在不用I2C总线配置寄存器的情况下也可提取出有效视频,因为在默认配置下ADV7183A输出的是8位BT656的YCrCb型4:2:2视频数据,可以根据BT656的标准提取有效视频,这样减少了编程工作,降低了FPGA与ADV7183A的连线,从而为FPGA控制其他芯片节约了引脚,提供了设计的灵活性。

1 设计方案

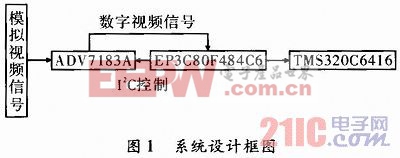

文中嵌入式数字图像采集系统的硬件结构如图1所示。在此视频采集系统中,采用Altera公司的Cyclone 3系列FPGA:EP3C80F484C6,AD公司的视频解码芯片ADV7183A,TI公司的TMS320C6416。模拟视频信号PAL制输入到ADV7183A中,由FPGA产生的I2C总线配置ADV7183A内部的寄存器,控制ADV7183A输出的像素时钟频率,行场复位起始位置、宽度以及数据宽度等。ADV7183A输出的数字视频信号经过FPGA的预处理传送到DSP,由DSP显示图像来验证隔点采样是否合理。

2 ADV7183A的设置

AD公司生产的ADV7183A是一款通用性强的视频解码芯片。芯片应用的关键就是要设置ADV7183A内部的一些寄存器,使ADV7183A能正常工作。而ADV7183A采用了I2C总线接口标准,所以对该芯片的控制主要是通过I2C总线的数据传输。

对于本系统而言,取默认配置,无需再对I2C总线进行配置,当ADV7183A正常工作后输出8位BT656的YCrCb型4:2:2视频数据,只需320×256的灰度图像,即取Y,而不要C,因此必须进行隔点采样。

(1)原理图设计方案:给复位,使能和27 MHz的时钟信号分别到![]() 引脚,

引脚,![]() 引脚,XTAL引脚,复位引脚和使能引脚都是低电平有效,通过FPGA控制这3个引脚来控制ADV7183A的工作。选择模拟输入通道AIN1,在AIN1引脚上输入模拟信号。完成这些设置后,接上电源,ADV71 83就可以在默认配置下正常工作,默认配置为:输入是PAL制的图像。输出是P8~P15的8位ITU—BT656的YCrCb型4:2:2视频数据,像素时钟是LLCC1:27MHz。

引脚,XTAL引脚,复位引脚和使能引脚都是低电平有效,通过FPGA控制这3个引脚来控制ADV7183A的工作。选择模拟输入通道AIN1,在AIN1引脚上输入模拟信号。完成这些设置后,接上电源,ADV71 83就可以在默认配置下正常工作,默认配置为:输入是PAL制的图像。输出是P8~P15的8位ITU—BT656的YCrCb型4:2:2视频数据,像素时钟是LLCC1:27MHz。

(2)对于输出的8位ITU—BT656,行数据由水平消隐,有效视频开始定时信号,有效行数据以及有效视频结束定时信号组成。帧数据由场消隐,第一场数据,场消隐和第二场数据组成。场消隐和场数据分别由若干行数据组成,消隐数据为0X8010,即在水平消隐和场消隐时一律用16进制的0X8010作为流数据。

有效视频开始(SAV)和有效视频结束(EAV)为两个定时基准信号,每个定时基准信号由FF 00 00 XY组成,前3个是固定前缀,第4个包含场标识,场消隐和行消隐状态的信息,其定义为:F为场同步信号,0其他情况,1表示场消隐;H为水平同步信号,0表示有效视频开始,1表示有效视频的结束,P0—P3称为保护比特,它们的状态取决于F,V,H的状态,如表1所示。

评论