基于AD9225的12位高速ADC的存储电路设计与实现

在高速数据采集中,高速ADC的选用和数据的存储是两个关键问题。本文介绍一种精度为12位、采样速率达25Msps的高速模数转换器AD9225,并给出其与8位RAM628512存储器的接口电路。由于存储操作的写信号线是关键所在,故给出其详细的获取方法。

本文引用地址:http://www.eepw.com.cn/article/194401.htm1 AD9225的结构

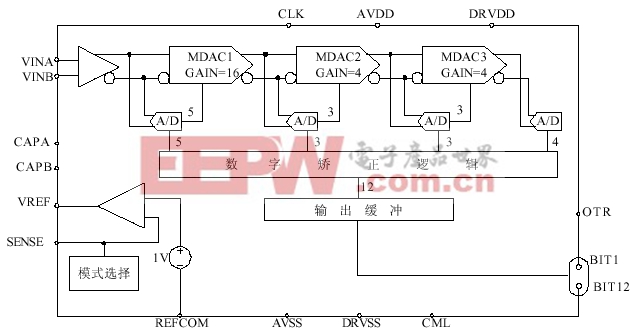

AD9225是ADI公司生产的单片、单电源供电、12位精度、25Msps高速模数转换器,片内集成高性能的采样保持放大器和参考电压源。AD9225采用带有误差校正逻辑的四级差分流水结构,以保证在25Msps采样率下获得精确的12位数据。除了最后一级,每一级都有一个低分辨率的闪速A/D与一个残差放大器(MDAC)相连。此放大器用来放大重建DAC的输出和下一级闪速A/D的输入差,每一级的最后一位作为冗余位,以校验数字误差,其结构如图1所示。

图1 AD9225结构图

2 AD9225的输入和输出

(1) 时钟输入

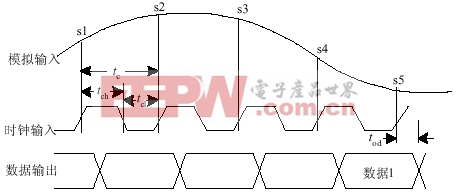

AD9225采用单一的时钟信号来控制内部所有的转换,A/D采样是在时钟的上升沿完成。在25Msps的转换速率下,采样时钟的占空比应保持在45%~55%之间;随着转换速率的降低,占空比也可以随之降低。在低电平期间,输入SHA处于采样状态;高电平期间,输入SHA处于保持状态。图2为其时序图。图2中:

图2 AD9225时序图

tch——高电平持续时间,最小值为18 ns;

tcl——低电平持续时间,最小值为18 ns;

tod——数据延迟时间,最小值为13 ns。

从时序图可以看出:转换器每个时钟周期(上升沿)捕获一个采样值,三个周期以后才可以输出转换结果。这是由于AD9225采用的四级流水结构,虽然可以获得较高的分辨率,但却是以牺牲流水延迟为代价的。

(2) 模拟输入AD9225的模拟输入引脚是VINA、VINB,其绝对输入电压范围由电源电压决定:

其中, AVSS正常情况下为0 V,AVDD正常情况下为+5 V。

AD9225有高度灵活的输入结构,可以方便地和单端或差分输入信号进行连接。采用单端输入时,VINA可通过直流或交流方式与输入信号耦合,VINB要偏置到合适的电压;采用差分输入时,VINA和VINB要由输入信号同时驱动。

(3) 数字输出

AD9225 采用直接二进制码输出12位的转换数据,并有一位溢出指示位(OTR),连同最高有效位可以用来确定数据是否溢出。图3为溢出和正常状态的逻辑判断图。

电子血压计相关文章:电子血压计原理

评论