基于FPGA的等位移多点采样硬币识别研究

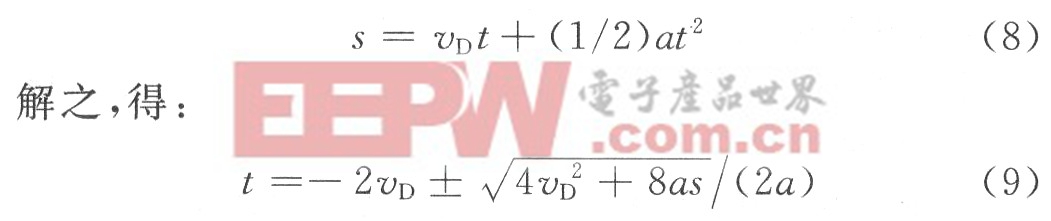

由于硬币在币道中做匀加速度直线运动,设硬币的前沿通过D点时的速度为vD,则有:

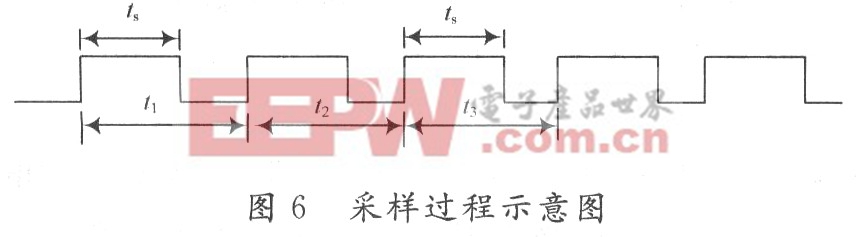

令s为0.1 mm,0.2 mm,0.3 mm,…,设需要的时间分别为t0.1,t0.2,t0.3,…。由2.3所述方法可求得a和vD,则通过求解一元二次方程可得到t0.1,t0.2, t0.3,…,若以硬币通过D点作为零时间参考点,则在t0.1,t0.2,t0.3,…采样即可得到正确的等位移多采样值。有:t1=t0.2-t0. 1,t2=t0.3-t0.2,…。

当硬币后沿通过E点时,停止采样,D点和E点的沿币道方向的距离为y,设通过E点的时刻为tE,则有:

由此即可计算出tE,即为硬币通过币道时最后一个采样点。

根据式(9),要求得t,涉及到开方运算。开方运算的算法主要有Newton-Raphson算法、SRT-Redun-ant算法和Non-Redudant算法。这三种算法可以得到开方运算的近似结果。关于上述三种算法的介绍参见参考文献[1―3]。

为了有足够高的检测精度,要求t精确到1μs。另外,由于硬币由C点到D点的最小时间为0.3 ms,所以必须在0.3 ms内完成上述的算法。通过FPGA不难实现这些要求,但是若采用单片机来实现就有一定的难度,如:若用51单片机,频率12 MHz来实现,则机器周期就是1μs,要实现上述算法是不可能的。所以在该设计中采用FPGA实现。

2.5 基于FPGA的多倍周期同步测频法

在该设计中,检测线圈为电涡流反射式互补检测,准确地测试出其输出频率是很重要的。对于频率的测试,有测频法、测周期法,但测量精度都不够高,在该设计中,两种测试方法误差都比较大,所以采用等精度多倍周期同步测频法,可达到较高的精度。

由于硬币通过检测线圈时的速度范围为:0.1~0.5 m/s,要求每隔0.1 mm距离采样一次,则采样的时间间隔范围为0.2~1ms。为了保证采样的快速和准确性,采样时间不能超过0.2 ms,本设计采样时间取0.1 ms。

该设计中,FPGA的频率为100 MHz,由检测线圈及检测电路组成的振荡器频率为200 kHz(此频率指硬币未通过线圈时的振荡频率)。

所谓测频法,就是先给定一个闸门时间,在此闸门时间内,对被测频率信号计数,由此即可计算出被测信号的频率。在本设计中,闸门时间为0.1 ms,被测信号频率为200 kHz左右,若用测频法,则测量误差为:

1/(0.1×10-3×200×103)=5%

所谓测周期法,就是在被测频率信号的一个周期内,对参考频率信号进行计数,由此即可计算出被测信号的周期,在本设计中,参考频率信号为100 MHz,被测信号频率为200 kHz左右,若用测周期法,则测量误差为:

(200×103)/(100×106)=0.2%

由此可见,都有较大的误差,下面用等精度多倍周期同步测频法,既可以在振荡频率变化的情况下保持精度的一致,又可以减少测量误差,提高测试精度。

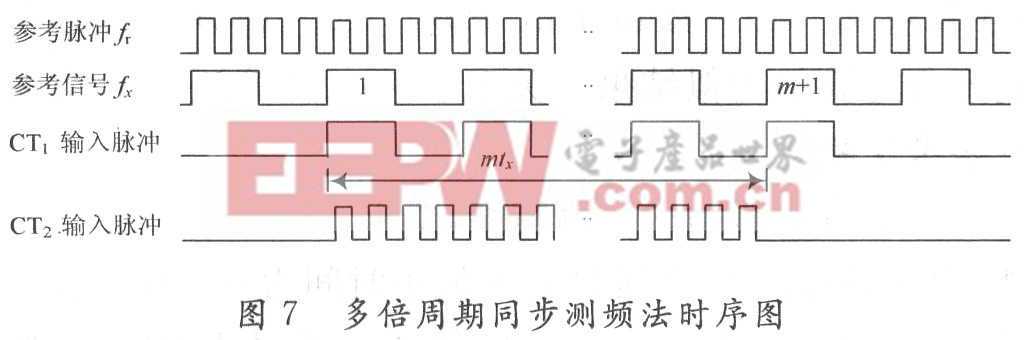

设被测信号频率为fx,计数器CT1对fx进行计数;参考信号频率为fr,计数器CT2对fr进行计数。

CT1的闸门开放时间完全与fx的m个周期同步。闸门开放时间T1=mtx。在fx的第一个上升沿和第m+1个上升沿之间的mtx时间间隔内,允许CT2对fr计数,计数值记为N。上述测频的时序图如图7所示。

fx的计算公式如下:

fx=m/Nfr

评论