基于FPGA的两路视频同步播放系统的设计

2.2.3重叠区域采样电路模块设计输入视频信号重叠区域采样窗模块是由两块uPD42280芯片串联构成。通过 FPGA对uPD42280芯片发出控制信号,达到对指定像素区域进行采样的目的。之所以采用两片 uPD42280芯片串联是考虑到系统设定的同步范围。对于 50HZ的PAL制的隔行扫描图像,每一场的采样像素点为32*32=1024个,只取其中 8位Y信号,则每一场的采样数据量为 28800字节。uPD42280场存储器的单片容量为 256K字节,可以容纳约 256场。这样采用两片串联增加了一倍的容量,采样窗的数目可以达到512场。

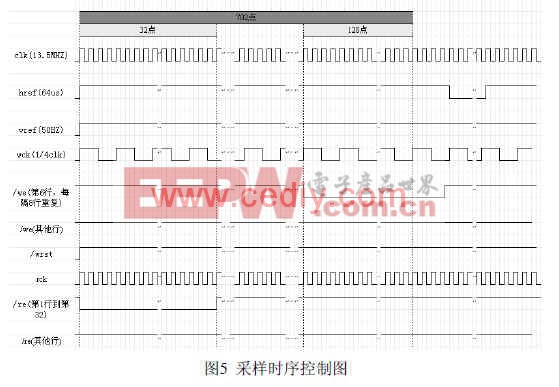

采样的控制时序图5所示,为了对 702*288的右1/4重叠区域进行行列的均匀采样,每隔 8行在后128点进行 1/4clk均匀抽样,得到 32点。同时,每场一共抽取 32行,这样 FIFO中存储数据为32*32=1024byte。而读时钟在每场的前 32行,采用clk(13.5MHZ)进行连续读取。图 6为一帧图像重叠区域采样的效果图。本文引用地址:http://www.eepw.com.cn/article/191936.htm

2.2.4存储器电路模块设计

在本系统中,由于需要用到大规模的图像数据存储及运算存储操作,并且考虑到系统算法的可扩展性,存储器选取了两片 SDRAM芯片 HY57V641620HG,每片 HY57V641620HG大小为 4bank*1M*16bit。在结构设计方面,由于 SDRAM不能够同时进行读写操作,与主控运算电路采取并行连接的方式。这样做的目的是可以进行 SDRAM的乒乓读写操作,提高数据读取及写入的效率。

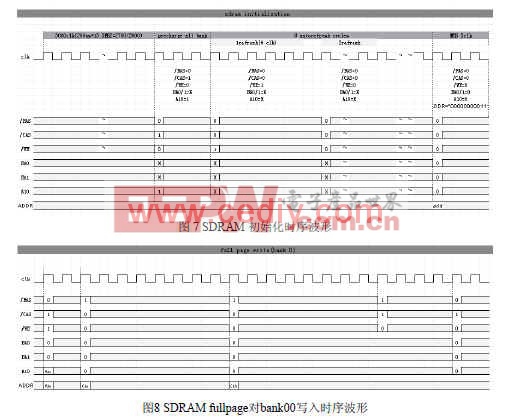

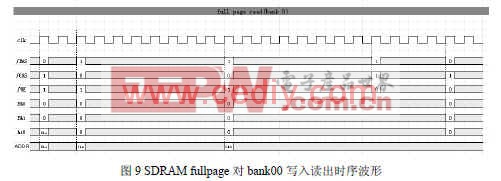

FPGA对SDRAM的初始化和fullpage模式下的读写控制的时序如图 7、8、9。

2.2.5 FPGA主控运算电路模块设计主控运算电路是本系统中最重要的硬件组成部分,因为这部分电路将承担整个系统大部分控制和运算任务。这部分电路由 FPGA芯片 EP1C6及其附属电路组成。

评论