基于FPGA的两路视频同步播放系统的设计

2.1 硬件系统总体设计

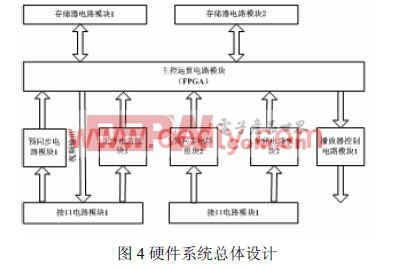

如图 3.1所示,两路视频同步播放系统由接口电路、输入视频信号预同步电路、输入视频信号重叠区域图像采样窗电路、数据存储电路、主控运算及播放器控制电路组成。

本文引用地址:http://www.eepw.com.cn/article/191936.htm

本文引用地址:http://www.eepw.com.cn/article/191936.htm2.2 主要硬件功能模块电路设计与测试

2.2.1 接口电路模块设计

接口1和接口2分别将两路视频信号由播放器引入后续处理模块,并将处理后的视频信号输出给显示系统。

2.2.2 预同步电路模块设计两路输入视频信号在进行同步处理前需要首先进行缓冲,以期在同一时刻到达主控模块上一致。本系统采用两片有 FPGA芯片控制的 FIFO芯片分别实现两路信号的预同步功能。

本系统采用uPD42280芯片。 uPD42280是容量为256kbyte*8bit (262, 224 * 8bit)的高速场存储器。CMOS动态电路实现了芯片的高速和低功耗。 uPD42280O可以设置为同步或异步读写的FIFO。其中, DI0-7为数据输入,DO0-7为数据输出;/WE、/RE分别为写使能和读使能; /WRST、/RRST分别为写复位和读复位; VDD、GND分别为电源和接地。而在进行预同步处理时,两路输入的视频信号均为隔行PAL制黑白信号,其中亮度信号为8位,即每帧图像大小为702*288*8/1024/8=198Kbyte,所以 uPD42280的容量足够一场图像的存储。

评论