基于FPGA的PLL频率合成器设计

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。同时FPGA也实现了键盘扫描与液晶显示的功能。

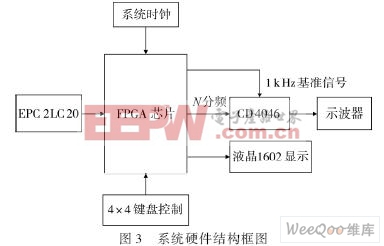

2.1 系统硬件设计

硬件上,如图3所示。该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。本设计使用FPGA专用配置芯片EPC2,通过下载电缆ByteBlaster MV,把程序多次下载到FPGA芯片中。系统使用FPGA芯片作为控制中心,按键扫描输入控制信息,液晶屏进行显示,能够方便直观地演示PLL芯片CD4046在频率合成技术中的应用,且达到了预期的指标要求。本设计中的主要硬件的具体型号是:液晶TC1602A-01T,FPGA芯片EPF10K10LC84-4,40.000 MHz有源晶振HO-12B。

2.2 系统软件设计

通过编写VHDL程序实现整数/半整数分频,并应用Quartus II和ModelSim,笔者完成了VHDL程序的设计及仿真。

系统软件功能框图如图4所示。

系统的具体工作过程如下:

键盘扫描模块负责扫描按键,输出键值,键值输入到1602液晶模块中进行显示。同时,通过功能键模块去控制键值输入到FPGA中的分频模块中,功能模块为“确定”时,键值输入到FPGA分频模块中,分频系数N就等于输入的键值。功能模块为“清除”时,FPGA分频模块中,分频系数N就会被清零。

3 系统测试及结果

测试仪器:INSTEK GOS-620(20 MHz模拟示波器)

测试温度:室温

3.1 检测系统是否入锁

键盘输入从1~999.5时,所测CD4046的1号管脚波形如图5所示,指示PLL处于入锁状态。

3.2 检测较低频的整数/半整数分频

当N=3、9、13、1.5、5.5、9.5,输入为1 kHz的频率时,CD4046的输出波形分别如图6(a)、(b)、(c)、(e)、(f)、(g)所示。从图中可以很明显地读到,输出分别为3 kHz、9 kHz、13 kHz、1.5 kHz、5.5 kHz和9.5 kHz。这与理论上预见的结果是一致的。

评论