采用中档FPGA设计面向PCI Express系统的解决方案

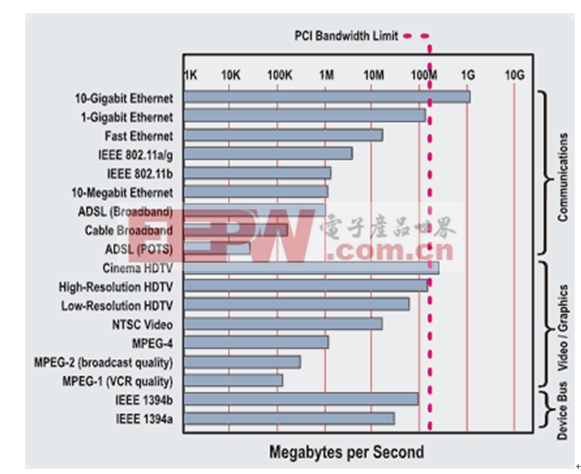

为了克服旧标准的上述局限,1992年人们建立了PCI。其目的是构建一个更高带宽的标准,有即插即用功能和更稳健的协议。PCI协议支持差错校验,通过与计算机的BIOS(基本输入输出系统)通信实现即插即用功能,并通过标准的控制/状态软件接口就地址范围或PCI插卡功能等信息进行交换。如果出现地址范围重叠等差错,计算机本身可以提供一些反馈。一个基本的32位33MHz的PCI系统,可支持的传输速率高达132MBps。但是,这个架构也有一些限制因素。总线是单向的(发起方和被请求的目标设备不能在同一时间进行通信),且几个卡要共享一条总线。如果一张卡正在传输数据,所有其他的可访问总线的部件必须等待。此外,在系统中无法处理PCI带宽的低性能卡将进行“重试”请求,以确保有更多时间来处理数据。这就大大降低了整个系统的带宽。PCI的另一个限制是各种应用对所需求带宽不断增加,特别是在视频、通信和总线领域。图1列出的一些应用,已经接近或超过了理论上的PCI带宽132MBps。

本文引用地址:http://www.eepw.com.cn/article/191824.htm

图1:各种应用的带宽需求对比理论上PCI提供的132MBps。

PCI还有其他一些缺点,如限制只能有5个部件访问总线。由于PCI总线特殊的无端接总线的反射,电路板的设计也更加困难。数据路径宽度为32或64位的并行线也对时序有苛刻的要求。

根据以往经验,PCI-SIG(PCI特别兴趣小组)与行业内的领先公司合作,定义了PCI的下一代标准。新标准最初被称为3G IO(第三代输入输出),后来改名为大家熟悉的PCI Express。PCI Express的首个规范于2002年4月公布,其解决了原有PCI标准的所有限制因素。为了克服无端接的大量并行总线并增加带宽,PCI Express转变为运行速率2.5Gbps的串行链路,提供两个方向同时进行的2Gbps的原始数据率。为了满足更高的带宽要求,规范允许使用几个并行的“通道”。因此对于目前计算机的低带宽应用,有很多x1和x4通道;对于有高带宽的要求,例如显卡,则有x16的插槽。

由于PCI Express规范使用基于层的协议,类似于OSI的层次模型,它很容易改变物理层和保留上层协议。这种做法已被最近发布的PCI Express 2.0规范所采纳,使得链路速度高达5Gbps。然而,大多数新的设计开始仍然是基于PCI Express 1.1版本的2.5Gbps。

一个PCI Express系统可以用几个部件组成。所有的系统都需要有一个根联合体(Root Complex)对整个系统进行管理。交换设备(Switch)是用来将几个卡连接到另一个PCI Express链路,“端设备”则代表了用户应用。桥接是端设备的特殊形式,可以将旧的PCI应用连接至PCI Express总线。FPGA主要用于端设备或桥接应用。

在PCI Express应用中FPGA起着重要的作用,主要有三种设计方法:

*PCI-Express至PCI桥和FPGA

*外部的PCI-Express PHY和FPGA

*PCI-Express的PHY集成在FPGA之中

第一种使用PCI-Express至PCI桥的方法,优点是可以重用旧的PCI设计,但由于额外的桥接单元,成本很高。在桥和FPGA之间,这个应用仍然被PCI的缺点所限制,在成本方面处于不利地位。

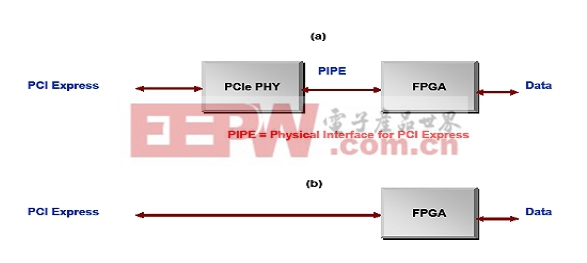

图2A和2B

当仅需纯粹的PCI Express接口,而不需要其它逻辑时,外部的PCI Express PHY和FPGA(图2A)相结合可能极具吸引力。利用被称为PIPE的并行接口,PCI Express PHY可以连接到FPGA。虽然PIPE接口被认为是一个标准,但不同厂商在实现方面有着细微的差别,因此物理层芯片就不容易互换。此外,工业级的外部PCI Express PHY芯片也不太容易买到,要不就是价格昂贵。此外,许多应用程序使用领先的器件,可用的领先的PCI Express PHY芯片也是很有限的。

因此,如果只有一个PCI Express接口链路,而且在FPGA中只要少量的额外逻辑(除了温度范围的限制,以及可用的领先器件),这种做法颇有意义。对于所有其他应用,最好是考虑一个整合的解决方案,如图2B所示。

评论