基于FPGA的SPI总线接口的实现

0 引言

串行接口已成为当前传输接口的发展趋势,原因在于串行的高速率传输性能和较简单的线路连接。在已知的外围器件连接端口中,有USB,wishbone和并行端口。其中SPI接口总线基于串行传输的思想,已经制定成为标准,成为常用的外围器件连接方式。针对FLASH这种常用的外围存储器件,有多种接口可供选择,然而具有SPI接口的FLASH芯片硬件连接方便,通过FPGA编程可以便捷地实现FLASH的存取功能。因此基于FPGA的具有SPI总线接口的FLASH功能实现为工程设计提供了一种原型,为进一步的工程开发奠定了基础。

1 SPI总线介绍

1.1 SPI总线简介

同步外设接口(serial peripheral,interface,SPI)是由摩托罗拉公司开发的全双工同步串行总线。SPT是一种串行同步通信协议,由1个主设备和1个或多个从设备组成,主设备启动一个与从设备的同步通信,从而完成数据的交换。

1.2 SPI总线接口及时序

SPI接口由SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS(从使能信号)四种信号构成,CS决定了惟一的与主设备通信的从设备,如没有CS信号,则只能存在一个从设备,主设备通过产生移位时钟来发起通信。通信时,数据由SDO输出,SDI输入,数据在时钟的上升沿或下降沿从SDO输出,在紧接着的下降沿或上升沿由SDI读入,这样经过8/16次时钟改变,完成8/16位数据的传输。

在SPI传输中,数据是同步进行发送和接收的。数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI时钟规范。然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数;CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于数据位的时钟相位。CPOL和CPHA的设置决定了数据取样的时钟沿。

SPI模块为了与外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有大的影响。如果CPOL=0,串行同步时钟的空间状态为低电平;如果CPOL=1,串行同步时钟的空间状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设时钟相位与极性应该一致。SPI接口时序如图1所示。

2 基于FPGA的SPI接口设计

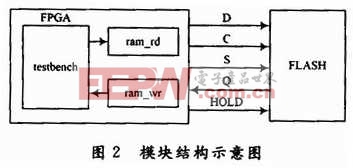

SPI接口适用于主芯片与从芯片的连接,在一个FPGA系统中,充当主芯片的为FPGA可编程芯片,而FLASH芯片作为外围从芯片通过SPI接口连接至FPGA芯片。该系统选用Lattice公司的FPGA芯片,该公司的产品线齐全,其中ECP2M系列芯片功能全面,开发成本低廉。ECP2M系列芯片支持SPI接口,通过硬件电路的简单设计即可完成SPI接口的物理连接,进一步利用Lattice的工程开发EDA软件进行FPGA编程,实现SPI接口控制。对接口的设计采用RAM作为读/写缓冲,完成主程序和FLASH之间的数据交换,各模块结构示意图如图2所示。

图2中ram_wr写端口数据宽度设置为32位,地址深度设为128位;读端口为1位位宽,这是由SPI端口的串行性决定的;ram_rd读端口与ram _wr写端口相对应。RAM模块如图3所示。

3 SPI接口实现及FLASH功能验证

3.1 M25P64串行FLASH芯片介绍

M25P64串行芯片由STMicro公司生产,它具有64 Mb容量,最高时钟频率可达50 MHz同时采用SPI总线接口。该FLASH芯片的存储空间划分为128区,每区为65 536 B。在芯片中,其中D为数据串行输入端;C为时钟输入;![]() 为低电平有效片选信号;

为低电平有效片选信号;![]() 和

和![]() 分别为写保护和暂停保持输入,Q为串行输出端。该芯片的指令丰富,功能完备,常用的指令如:读/写使能、读/写状态寄存器、读数据、页编程以及区块擦除等。

分别为写保护和暂停保持输入,Q为串行输出端。该芯片的指令丰富,功能完备,常用的指令如:读/写使能、读/写状态寄存器、读数据、页编程以及区块擦除等。

fpga相关文章:fpga是什么

评论