基于FPGA的SPI总线接口的实现

该芯片由一个微控制器控制,SPI接口有种工作模式分别为;CPOL=0,,CPHA=O和CPOL=1,CPHA=1,两者区别为在SPI主端不传数据时,时钟的电平前者为0,后者为1。在里采用CPOL=0,CPHA=模式。

3. 2 工程环境设置及SPI接口设计

Lattice公司的FPGA工程开发EDA软件名为ispLEVER,其7.2版本为较新版本。该版本集合了IPExpress,Reveal Logic Analyzer等实用工具,可用于添加Lattice公司开发的IP核以及在线逻辑仿真等。ispLEVER 7.2的默认仿真工具为Active-HDL仿真器,由于需要采用Model-Sim仿真器,因此安装ModleSim 6.2b版本。对仿真软件成功安装后,加入pcsc_mti_work,pcsc_mti_work_revA,ecp2m_vlg和pmi_work四个仿真库并进行编译。编译完成后启动ispLEVER 7.2,在options菜单中修改环境变量和默认仿真工具,使得ModelSim连接图标出现在工具栏中成为工程的仿真工具。

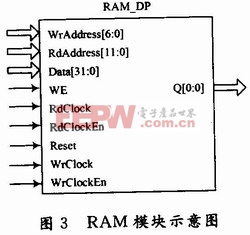

进入ispLEVER 7.2的编辑界面,开始建立工程,首先选择器件型号,这里采用LatticeECP2M系列中的LFE2MSOE型号芯片,并选择封装类型为FPGAB-GA672,速度级别为-5。器件选定后,建立FLASH_contro]工程文件和testbench测试文件,同时用IP Express生成读/写RAM模块。

在主程序中编写RAM控制段和SPI接口控制程序段,用状态机完成对RAM的控制,状态机在idle,read,write和config之间跳转。在向FLASH写数据时,应先写入写使能指令,完成后写入页编程指令,随后写入地址,最后写入数据;从FLASH读数据的过程大致相同,但应首先写入读使能指令,然后写入读数据指令。应当注意的是读指令的时钟频率低于写指令,具体频率要求可参照芯片说明手册。

3.3 SPI接口功能验证

在线逻辑分析仪(reveal logic analyzer)是较为先进的EDA工具,它能提类似于功能仿真的波形示意图,这些波形是通过在FPGA芯片运行过程中实时抓取出来的。它真实地再现了FPGA芯片内部的动态信号状况,使工程开发人员能直观的发现问题,修正逻辑。仿真综合通过后,将程序下载至FPGA芯片中,用Reveal Inserter插入在线逻辑分析信号,采样点数设定为2 048个点,分析信号会在工程目录中生成一个相关文件,综合后将数据文件下载至Lattice芯片中,采用人工触发后,即可在在线逻辑分析仪中观察信号波形。截取的波形如图4所示。

从图4可看出,在时钟C的8个有效周期写入写使能指令,写使能指令通过D信号线串行进入FLASH芯片,指令的写入过程应保证S信号低电平,8个周期的指令输入完毕后S回复为高电平。在SPI总线主端的RAM控制信号由状态机控制,instructions为8位的寄存器,用于存储指令;RAMl_dout对应ram_wr的输出端口。

图5为数据指令后读出数据的波形图,数据从Q信号线读出并进入ram_rd。在读数据周期S保持低电平,数据的输出在时钟的下降沿发生,在读指令完成后,state状态寄存器回复至空闲状态。

4 结语

SPI总线是当前流行的串行接口的一种,它满足工程设计的要求,使开发人员能够简单迅速的完成设计工作,实现功能要求。将它与FPGA编程结合,利用FPGA的灵活性,使电子设计能够在很短的周期内完成,符合当今电子设计的要求。本文通过实现带有SPI总线接口的FLASH芯片功能,验证了基于FPGA设计的SPI接口的正确,实现了FLASH芯片的读/写功能。

fpga相关文章:fpga是什么

评论