基于HyperLynx的FPGA系统信号完整性仿真分析

串扰是信号完整性问题之一,它是指有害信号从一个网络转移到相邻网络。串扰可分为近端串扰(NEXT)和远端串扰(FEXT),传输线的反射跟串扰也有联系,采用合适的源端端接和远端端接可以在一定程度上减小串扰。但串扰与信号之间的容性耦合和感性耦合有关,串扰不可能完全消除,只能减小。在TMS320F2812和EP2C8之间有大量的高速数据线,如果不进行处理则有可能接收错误的数据。图4所示为用LineSim对数据线D8,D9和D10进行SI仿真的结果,设定D9是被干扰的网络,D8、D10是攻击网络,振荡频率为20 MHz,端接电阻为50 Ω。从图可知D9受到的干扰较小,过冲电压只有122 mV。如果想要进一步减小串扰则可以减小走线宽度到8 mil,同时缩短走线耦合长度。本文引用地址:http://www.eepw.com.cn/article/191200.htm

3.2 高速信号线时序问题

TMS320F2812和EP2C8之间数据收发率高,因此时序就变得十分重要,如果两信号到达接收端的时差近似于一个采集周期将导致接收到错误的数据。为了避免这种时序可题的发生,通过蛇形线来保证高速信号走线长度的一致,如图5所示。PCB设计的工具是Altium公司的DXP 2004。

4 BoardSim仿真

BoardSim是在PCB绘制完成后进行的仿真,生成整版报告,验证原有设计的合理性、修正布局布线。仿真将利用器件的IBIS模型对已经设计好的PCB走线进行仿真,包括信号完整性、EMC、时序等。

4.1 串扰仿真验证

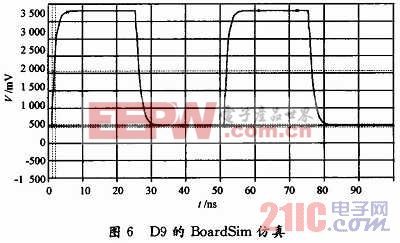

第3.1节中已经对D8,D9和D10进行了串扰仿真,现在用BoardSim来验证上述仿真结果。考虑到实际电阻值没有50 Ω,所以采用端接电阻值为51 Ω,振荡频率为20 MHz。图6所示为当D8,D10有数据通信时D9受到的干扰。由图可知,D9处的波形抖动很小,串扰电压过冲只有44.8 mV,下冲电压只有-39.8 mV,基本上不会影响D9的信号,结果表明已经通过信号完整性检查。

4.2 端接仿真验证

主要验证时钟信号和数据线的端接方案的合理性。

评论