基于HyperLynx的FPGA系统信号完整性仿真分析

3 LineSim仿真

LineSim可以在布局布线前对所设计的方案进行仿真,将仿真的结果作为实际布线的约束条件,在初期预测和消除信号完整性问题。

3.1 高速信号线端接仿真

信号反射的原因是信号沿导线传播所受到的瞬态阻抗发生变化时,则一部分信号将被反射,另一部分发生失真并继续传播下去,这将导致波形的边沿处发生振铃现象。一般要求过冲幅值限定在150 mV左右,否则会造成EMC问题。典型的端接方式包括:源端串联端接;远端并联端接;远端戴维南端接;远端RC端接。其中源端串联端接使用器件少并且效果好,因此该系统采用源端串联端接方案。

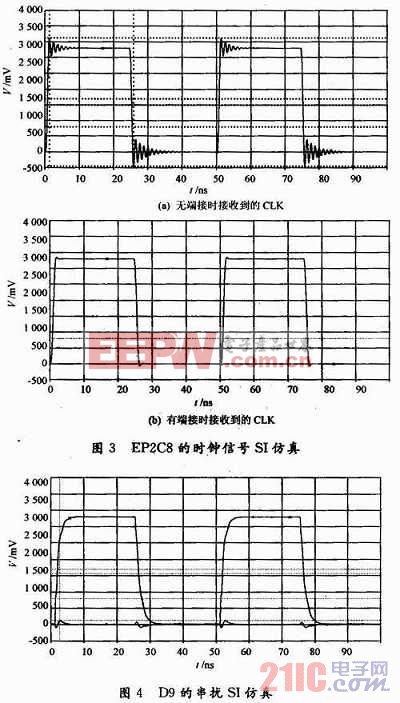

由于EP2C8采用20 MHz独立的有源时钟,因此在仿真时只需考虑EP2C8的CLK。若将有源晶振的输出直接和EP2C8相连,则LineSim仿真的结果如图3(a)所示,信号边沿处有振铃现象,电压过冲幅值3.629 V,下冲值为-450.2 mV,超过了过冲幅值范围。当采用一个阻值为50 Ω源端串联电阻时,SI仿真的结果如图3(b)所示,接收端接收到的时钟信号在跳变处无振铃现象,抑制信号反射的效果很好。本文引用地址:http://www.eepw.com.cn/article/191200.htm

评论