使用DS89C450对Xilinx PROM的在系统编程设计

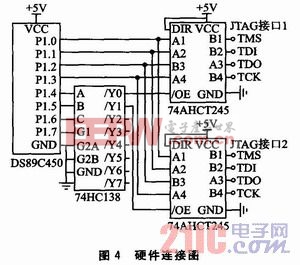

本设计中,硬件连接图如图4所示,每个JTAG接口都与一片74AHCT245相连,DS89C450的P1.0、P1.1、P1.2、P1.3分别对应TMS、TD-I、TDO、TCK的功能;而P1.4、P1.5、P1.6、P1.7通过译码器74HC138构造片选逻辑。当P1.7为低电平时,译码器74HC138所有的输出引脚/Y0~/Y7均为高电平,所有74AHCT245的/0E脚均为高,因此,所有的JTAG接口均未选中,这时,它们都可以通过Xilinx Impact软件进行操作。这个状态作为系统上电之后的默认状态。图4作为示意图,只画出了2个JTAG接口,而最多可以连接8个JTAG接口。本文引用地址:http://www.eepw.com.cn/article/191142.htm

当需要对某个JTAG连接的Platform Flash PROM编程时,上位机通过串口向DS89C450发出命令,DS89C450收到正确的命令之后,打开译码器的G1门,对8个JTAG接口进行扫描,将扫描到的IDCODE上报上位机,空的JTAG接口将扫描到全“1”码;然后,上位机送出需更新代码的板卡地址,DS89C450根据这个地址选择指定的JTAG接口(即选择了需要更新代码的PlatformFlash PROM),自动升级也就开始了。升级结束,关闭译码器的G1门,回到默认状态。

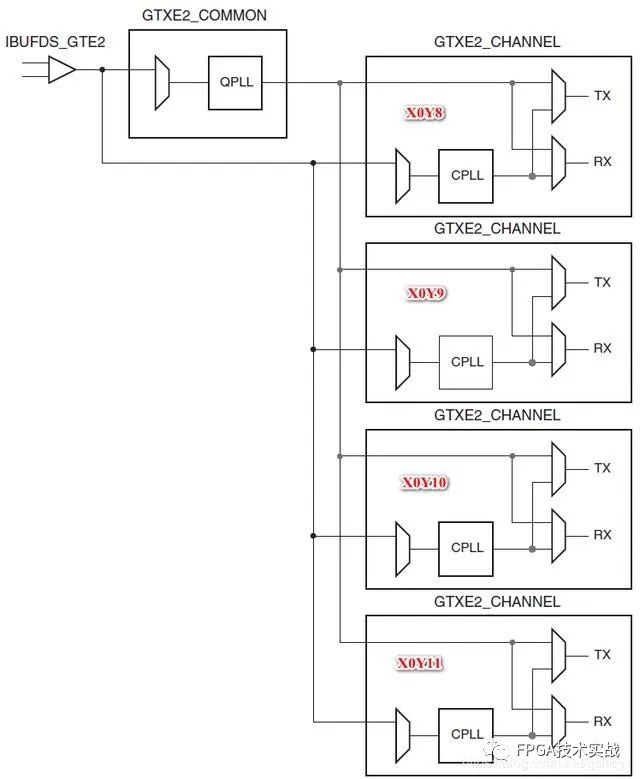

一般情况下,具体到某一块板卡,其上的JTAG插针,是将Platform Flash PROM的JTAG和FPGA的JTAG串联起来的菊花链结构。例如,插针的TDI→(TDI,TDO)→(TDI,TDO)→插针的TDO,用括号内的表示XCF01S或FPGA。因此,在图4中的JTAG接口指的是JTAG插针,而非某个具体器件的JTAG口。基于这一点,DS89C450要实现对Platform Flash PROM的操作,需要将菊花链中的FPGA旁路(bypass)。

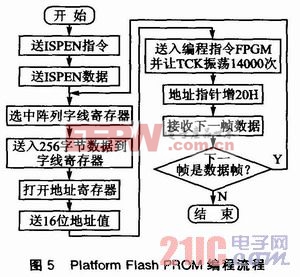

要对Platform Flash PROM的内容进行更新,上位机需将新文件(bin格式)按照一定长度的字节数分批次送给DS89C450,DS89C450将本次收到的定长数据写入Platform Flash PROM,写完之后,准备接收下一帧,依此往复,直到将新文件处理完。

对于XCF01S,其扇区大小为256字节,下面以每次传输256个字节为例,图5给出了操作Platform Flash PROM的指令及编程流程。表1为操作Platform FlashPROM的指令。

结语

本设计的优点是低成本、高性能、高灵活性。低成本体现在硬件上,用到的器件少,节省电路板空间;DS89C450是一款高性能的单片机,速度快,工作稳定;高灵活性体现在2个更新——一是可通过IAP程序更新DS89C450内部高32 KB区的用户程序,二是可通过DS89CA50内部高32 KB区的用户程序来更新Platform Flash PROM内的数据。同时,多片Platform Flash PROM的更新实现。这样,整个系统的更新维护将十分方便。

评论