基于CPLD系统的信号发生器设计

摘要:文中采用Quartus II开发平台,基于可编程逻辑器件CPLD设计出多波形信号发生器,可输出频率、幅度可调的三角波、正弦波和方波。任意波形模块可由用户输出用户所需的特殊波形,满足了教学实验和开发新的实验项目对特殊波形的要求。整个设计采用VHDL编程实

现,其设计过程简单,极易修改,可移植性强。另外,CPLD还具有可编程重置特性,因而可以方便地更换波形数据,且简单易行。

关键词:信号发生器:CPLD;D/A转换

CPLD复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围,是一种用户可根据需要而自行构造逻辑功能的数字集成电路。各种波形曲线均可以用三角函数方程式来表示,能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。函数信号发生器在电路实验和设备检测中具有十分广泛的用途。

1 系统设计

1.1 方案比较

方案1:直接频率合成法

直接频率合成技术即为用多个晶体分别产生不同频率的振荡信号,再经过具有四则运算功能的混频器、倍频器、分频器和不同频率的滤波器组合而成,用以实现特定频率信号的产生输出。

优点:频率转换时间短,理论上可产生任意小的频率间隔。

缺点:由于其利用晶体产生的信号经过运算而成,所以其频率间隔不能太多;由于采用了大量的倍频器、分频器以及混频器,所以其输出的波形信号附带的噪声较大;并且设备庞大,制造成本较高。

方案2:锁相频率合成

利用锁相环的良好的窄带跟踪性能,可使频率准确的锁定在参考频率或其N次谐波上,并使被锁定频率具有与参考频率一致的频率稳定度和较高的频率纯度。它由基准频率产生器和锁相环路两部分组成。

优点:结构简单,输出频率纯度高,易于得到大量的离散频率。

缺点:瞬时频率稳定度较差,频率转换时间较长。

方案3:直接数字频率合成技术(DDS)

直接数字频率合成技术完全摆脱了传统的频率合成技术的思路,即是通过对相位的运算来进行频率合成的,它的主要理论依据是Nyquist抽样定理对模拟信号进行采样,经量化后存入存储器中,再通过寻址查找表输出波形数据,经DAC及滤波后恢复原波形来实现频率合成的。

优点:利用DDS频率合成技术的器件功耗低,体积小,其工作频率范围宽,频率分辨率极高,频率转换时间极短。

缺点:由于受限于器件可用的最高时钟频率,输出频率上限不能太高;由相位量化噪声和幅度量化噪声所形成的总输出噪声电平很高。

1.2 方案选择

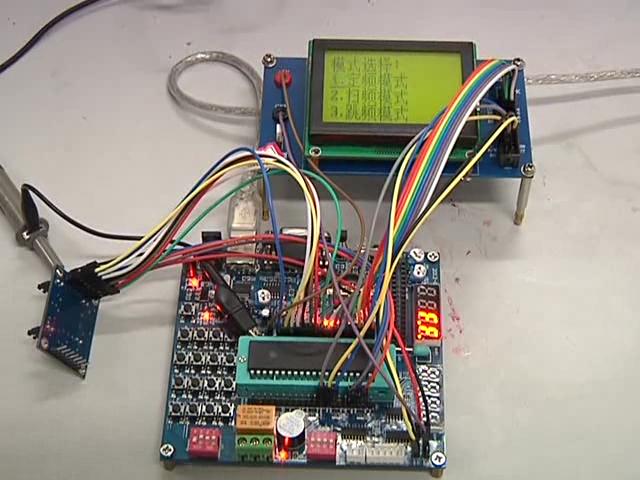

以上三种频率合成技术是现代频率合成技术的基础,在性能上各有特点,相互之间起到了很好的互补作用。本文综合三种技术采用的方案为:用CPLD开发板结合D/A芯片输出模拟信号,实现信号发生器功能。作为信号发生器时,能够产生三角波、正弦波和方波三种不同的波形,并且可以通过开发板上的按键来控制频率和波幅的调节。

1.3 方案的总体框图

图1所示为系统的整体框图。图1中,控制模块包括三个部分:外界输入、命令分析和输出指令。信号发生器模块也包括指令输入、选择波形产生和输出序列三个部分,其中在选择波形产生中决定选择波形的程序以及确定频率和幅度的大小。

评论