一种通用的FPGA位元电路

摘要:针对目前不同类型FPGA要求的位元电路不一致现象,提出了一种通用的FPGA位元电路,该位元电路不仅适用于任意结构的反熔丝/熔丝FPGA,还可以单独的存储1和0,对反熔丝/熔丝熔通后的电阻特性也没有具体要求。

关键词:现场可编程逻辑门阵列;反熔丝;位元电路;逻辑模块

FPGA (Field Programmable Gate Array), 即现场可编程逻辑门阵列,是当今集成电路半定制设计中的重要组成部分,具有结构灵活,功能完善,集成度高,设计周期短的特点,受到了越来越多的用户的欢迎;并且随着集成电路工艺制程的不断更新,FPGA的速度也得到了极大的提高。FPGA一般分为反熔丝型、EPROM型及SRAM型。

基于Flash的FPGA一般需要采用特殊的结构,造价很高;基于SRAM的FPGA器件虽然不需要特殊的工艺,可以用一般的CMOS工艺实现,但是这种FPGA的保密性及可靠性都不高;反熔丝/熔丝FPGA的保密性及可靠性都很高,市场上也有很多的反熔丝/熔丝结构,有些完全可以于CM OS工艺兼容。因此反熔丝/熔丝FPGA具有很好的发展前景。

在反熔丝/熔丝FPGA中,反熔丝/熔丝结构对FPGA的性能至关重要,这些反熔丝/熔丝结构击穿后的电阻特性不一致,大至10K欧姆,小的只有几欧姆,因此基于反熔丝/熔丝结构的位元电路需要单独设计。在本论文中提出的这种位元电路对反熔丝/熔丝结构击穿后的电阻没有特殊要求,因此具有重复利用性。因为篇幅有限,在此只叙述此位元电路在反熔丝FPCA中的应用,此位元电路可以完全应用到熔丝FPCA中。

1 新型反熔丝/熔丝位元电路

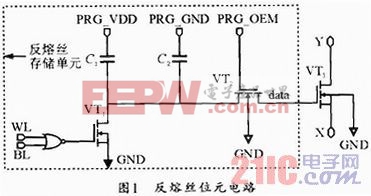

反熔丝/熔丝位元电路是控制反熔丝/熔丝完成逻辑编程的电路,图1所示是反熔丝位元电路,实框中是反熔丝存储单元电路图,该存储单元可以单独的存储0和1。写状态时加编程高压,让其中一个反熔丝电容熔通为一个小电阻,另一个反熔丝电容保持原状态;读取时,在熔通电容一端加电源电压,通过熔通后的小电阻传输高电平,完成1的存储;在熔通电容一端加低电平,通过熔通后的小电阻传输低电平,完成0的存储。可见位元电路输出高低电平是根据节点电压的变化来判断,与节点电流没有关系,因此对击穿后的电阻特性没有特殊要求。

对于熔丝位元电路只需将反熔丝结构换成熔丝结构,写状态时加编程高压,让其中一个熔丝熔断,另一个熔丝保持常态;读取时,在保持常态的熔丝一端加电源电压,通过熔丝传输高电平,完成1的存储,在保持常态的熔丝一端加低电平,通过熔丝传输低电平,完成0的存储。

图1的框外是一个MOS管,此MOS管是作为开关用的,当data输出0时,此开关关闭,X0与Y0断开,当data输出1时,此开关打开,X0与Y0实际上是连在一起的,此时从X0输入信号,Y0的输出信号即为X0。

DIY机械键盘相关社区:机械键盘DIY

评论