基于FPGA的异步串行总线设计

摘要:高速异步串行总线在现代通信设备中应用越来越广,文中介绍了一种基于FPGA的高速异步串行总线设计,详细描述了硬件设计和总线协议的实现方法。在现代通信系统的应用中有较高的实用价值。

关键词:异步串口;FPGA器件;Verilog HDL

随着近代通信技术的迅猛发展,对总线传输速率的要求也越来越高。传统的并行总线在发展到一定速率后很难再有所突破,并且在实际应用中还存在着大量的弊端,比如:成本相对较高、抗电磁干扰能力低下、模块间的总线互联繁琐等等。这些都给串行总线的发展和应用提供了客观动力。串行总线按传输模式可分为同步串行总线和异步串行总线两类;同步串行总线存传输过程中需要携带同步时钟信号,因此在传输距离较长或传输速率较高时会出现由于时钟衰落而引起的误码现象,制约了串行总线的传输速率和作用距离。而异步串行总线恰恰规避了这些缺点。因此异步串行总线被大量的应用于高速串行通信系统中。异步串行总线的按实现方式大致可分为两种,一种是采用专用串行总线接口芯片实现,实现方便简单,但二次开发性差,不利于系统升级维护;另一种是基于FPGA等可编程逻辑芯片实现。后者设计灵活,二次开发型良好,参数配置便捷,利于系统升级维护。本文将详细描述一种基于FPGA芯片硬件设计,采用Verilog HDL硬件描述语言实现传输协议的高速异步串行总线设计。

1 硬件设计方案

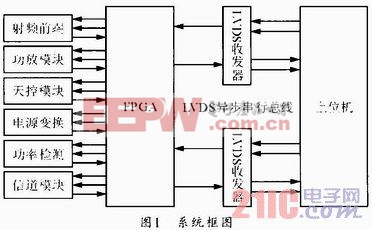

本设计通过高速异步串行总线和上位机进行通信,通过解析消息内容完成对下位机的实时控制与监测,并且将监测数据及时准确的回传至上位机本系统要求具备较高的实时控制性能,下位机响应上位机指令要求时间在3us以内,模块间通信稳定可靠、级联简洁,系统性能升级方便等。通过对系统要求研究分析,采用高速异步串行总线实现模块间通信比较符合要求。系统框图如图1所示。

高速异步串行总线碗件设计采用了以FPGA芯片为主,配以接口、时钟、电源变换等外围电路的设计思路。选用ALTERA公司的Cvclone系列FPGA作为核心器件。此芯片内部有丰富的逻辑资源和存储资源,有丰富的时钟网络和锁相环单元和I/O引脚,能够满足异步串行协议实现的硬件需求多种电压单独使用,有效降低芯片功耗。为了提高FPGA工作稳定性和可靠性在硬件设计时专门在其外围配置了电源监测电路和复位电路,对FPGA的各种工作电压和电流进行监测,当任意一路电压值发生突变时,电源监测电路都会给出命令,立刻关掉其它电源,或者将FPGA的供电端短路至地端,使FPGA进入断电状态,确保芯片不会被损坏。当电压值恢复正常时,电源监测电路将打开供电电路使FPGA再次进入工作状态,通过复位信号启动FPGA的程序从起始状态开始工作,确保FPGA芯片的物理安全和运行安全,从而有效提高系统的可靠性。设计中还采用了LVDS(Low Voltage Differential Signaling)收发芯片来提高串行总线的驱动能力。单端串行总线从FPGA输出后经LVDS收发器转化为差分信号线对输出至模块端口,与其它模块进行物理连接。串行总线采用差分线的连接方式能够更有效的抵抗传输中的共模噪声,降低传输误码率,大幅提高通信质量。详细的设计框图如图2所示。

评论