基于CPLD的双口模块设计

摘要:文章介绍了设计Multibus双口模块的方法。通过采用CPLD技术来实现模块内部逻辑,简化了模块的逻辑电路设计,提高了整个模块的稳定性和可靠性。达到了优化传统Multibus总线模块采用逻辑门电路和触发器来实现内部逻辑的目的。

关键词:Multibus总线;复杂可编程逻辑器件;双口RAM

0 引言

Multibus总线自1974年INTEL公司推出以来,以其自身支持集中式并行多处理、可靠性、抗干扰能力强等特点被广泛应用于工业控制领域和国防建设领域。但随着电子计算机技术的飞速发展,电子器件自身工艺、信号完整性等各方面不断提高,早期设计的Multibus总线模块通过逻辑门电路和触发器来实现内部逻辑的方法显然已经不能满足要求。随着EDA技术的广泛应用,CPLD技术己成为现代数字系统设计的主要手段,CPLD的时钟延迟可达到ns级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景。并且CPLD具有高集成度、高可靠性,几乎可将整个设计系统下载于同一芯片中,实现所谓片上系统,从而大大缩小其体积。CPLD目前正朝着更高速、更高集成度、更强功能和更灵活的方向发展。采用CPLD来实现Multibus系统模块的设计,不但节省电路开发费用,而且能提高设计效率,同时还能有效实现电路的数字化与微型化。

1 双口存储器的概念

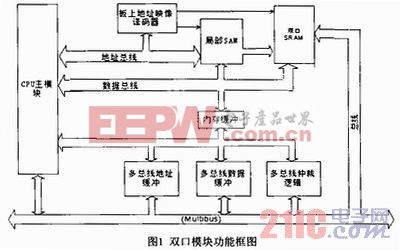

双口,既可以通过Multibus总线访问的存储器,又可以通过局部总线访问的存储器。双口RAM为硬件双口芯片,有两组独立的数据线、地址线和控制线。一组总线与主模块的局部数据、地址总线相连,另一组总线与Multibus数据、地址总线相连。主模块可以像读写局部RAM一样访问双口RAM,多总线上其他主设备也可通过该主模块的总线接口对双口RAM进行读写。两条数据总线也可以同时对某一存储单元进行访问。双口模块功能框图如图1所示。

Multibus总线系统容易构成多机系统,连于总线上的各个模块之间可以进行数据传输。在Multibus总线系统中,有着严格的时序要求,在控制信号启动之前50ns,地址必须形成。

设计时要结合考虑模块在现有系统中工作时,整个系统的时序,以及主从模块交换数据时,竞争总线时冲突等问题。

在多处理器系统中,为提高系统的吞吐率,避免因多个微处理器和存储器、I/O接口共用一组系统总线频繁存取时,造成系统“阻塞”,建立局部总线。局部总线有两个基本组件,一个是基板,一个是扩充模块。基板是指主控设备,扩充模块的作用主要是给基板提供专用功能。通过局部总线可以完成很大一部分存储器读/写操作和输入/输出操作。这样,只有在访问公共存储器和公共输入/输出接口时,采用系统总线。于是,避免了“堵塞”现象,而且还提供了各个子系统并行工作的条件。

而两路总线在一个系统中同时工作时,主模块对扩充模块可以从Multibus总线和局部总线两路访问,到底哪路总线访问扩充设备,这就是我们需要考虑的两路总线的优先裁决问题。

早期的模块中通过GAL器件编码、和多个触发器多总线仲裁电路。而应用中,对存储器的双口访问存在竞争现象。那么怎么来解决双口竞争问题呢?首先我们采用硬件双口芯片RAM,它有两组独立的数据线、地址线和控制线。一组总线与主模块的局部数据、地址总线相连,另一组总线与Multibus数据、地址总线相连,再就是采用CPLD技术实现内部逻辑,主模块可以像读写局部RAM一样访问双口RAM,多总线上其他主设备也可通过该主模块的总线接口对双口RAM进行读写。两条数据总线也可以同时对某一存储单元进行访问,而不产生竞争现象。

2 设计实现

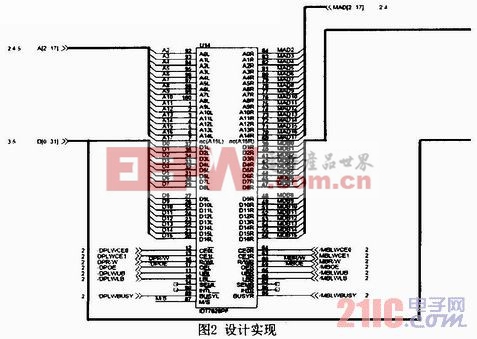

内部时序及逻辑控制电路主要由CPLD器件编程实现。采用的CPLD芯片为ALTERA公司的EPM7256SRI208-10芯片,其最高运行频率为227.3 MHz。采用MAX+PLUSII 10.0软件工具开发。设计完成板内地址总线、数据总线的控制信号;双口RAM的读写访问、片选信号、逻辑延迟应答信号等。设计输入完成后,进行整体的编译和逻辑仿真,然后进行转换、延时仿真生成配置文件,最后下载至CPLD器件,完成结构功能配置,实现其硬件功能。其中CLK时钟端口采用了常时钟信号/CCLK。/CCU是一个10MHz时钟,在应答生成逻辑上使用。

双口存储器可以通过Multibus总线和局部总线两路总线访问。由于采用硬件双口芯片,避免了两路总线同时在系统中工作时的竞争冲突问题。还可以在不同的用户环境中,只需更改跨接线的配置就可以满足,不需再重新编码,更改芯片配置。

在本设计中采用的双口存储器芯片为RAMIDT7027S25PF,是IDT公司研制的32k×16位的双口静态RAM。计算机主模块可以通过Local bus接口或Multibus接口对双口RAM进行读写。两组数据总线也可以同时对某一存储单元进行访问,而不产生竞争现象。设计实现如图2所示。

在双口RAM的两套控制线中,各有一个BUSY引脚。当两端的CPU对双口RAM的不同地址单元存取时,BUSYL=H、BUSYR=H,可正常存储;当两端的CPU对双口RAM同一地址单元存取时,哪个端口的存取请求信号出现在后,则其对应的BUSY=L,禁止其存取数据;在无法判定两个端口存取请求信号出现的先后顺序时,控制线BUSYL、BUSYR只有一个为低电平。这样,就能够保证对应于BUSY=H的端口能进行正常存取,对应于BUSY=L的端口不能存取,从而避免了两个CPU同时竞争地址资源而引发错误的可能。具体逻辑和电状态关系见表1。

3 需注意解决的问题

(1)输入、输出匹配问题。Multibus总线上所有信号都是低电平为现役的。器件输入输出电平在特定电压范围内为逻辑0或为逻辑1。

(2)测试需充分。必须用测试台对它的功能做到充分准确的测试。对该存储模块的容量和数位在单地址和连续地址下实现读、写功能。能正确实现对32k×16为存储单元写入任何数,完成数据正确性检查,进行可靠性连续考核试验。运行于多机环境中,通过两路总线随时访问任何单元,读写准确无误。

(3)时序问题。采用双口RAM来设计存储器模块时,会产生逻辑控制,读、写逻辑上的差异。因此在设计时应该严格控制模块的时序关系。

(4)配置可选。根据应用环境的不同,可灵活更改相应的配置。在本模块设计中就是通过配置跨接线来达到不同用户的需求。通过修改跨接线,即可调整存储器的地址空间,也可以根据需要来选择开放或关闭双口存储器,可根据多总线主设备的性能调整存储器的访问延迟时间。

4 结束语

经过实际测试,本模块通过采用硬件双口芯片及CPLD技术控制内部时序关系,解决了存储器访问竞争问题,通过可选跨接线配置,解决了多用户使用环境问题。提高了整个应用系统的可靠性。

评论