PCB的设计基础介绍

本文引用地址:http://www.eepw.com.cn/article/189877.htm

71、PCB 设计中,如何避免串扰?

变化的信号(例如阶跃信号)沿传输线由 A 到 B 传播,传输线 C-D 上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿的变化(转换率)越快,产生的串扰也就越大。空间中耦合的电磁场可以提取为无数耦合电容和耦合电感的集合,其中由耦合电容产生的串扰信号在受害网络上可以分成前向串扰和反向串扰Sc,这个两个信号极性相同;由耦合电感产生的串扰信号也分成前向串扰和反向串扰 SL,这两个信号极性相反。耦合电感电容产生的前向串扰和反向串扰同时存在,并且大小几乎相等,这样,在受害网络上的前向串扰信号由于极性相反,相互抵消,反向串扰极性相同,迭加增强。串扰分析的模式通常包括默认模式,三态模式和最坏情况模式分析。默认模式类似我们实际对串扰测试的方式,即侵害网络驱动器由翻转信号驱动,受害网络驱动器保持初始状态(高电平或低电平),然后计算串扰值。这种方式对于单向信号的串扰分析比较有效。三态模式是指侵害网络驱动器由翻转信号驱动,受害的网络的三态终端置为高阻状态,来检测串扰大小。这种方式对双向或复杂拓朴网络比较有效。最坏情况分析是指将受害网络的驱动器保持初始状态,仿真器计算所有默认侵害网络对每一个受害网络的串扰的总和。这种方式一般只对个别关键网络进行分析,因为要计算的组合太多,仿真速度比较慢。

72、导带,即微带线的地平面的铺铜面积有规定吗?

对于微波电路设计,地平面的面积对传输线的参数有影响。具体算法比较复杂(请参阅安杰伦的EESOFT 有关资料)。而一般 PCB 数字电路的传输线仿真计算而言,地平面面积对传输线参数没有影响,或者说忽略影响。

73、在 EMC 测试中发现时钟信号的谐波超标十分严重,只是在电源引脚上连接去耦电容。在PCB 设计中需要注意哪些方面以抑止电磁辐射呢?

EMC 的三要素为辐射源,传播途径和受害体。传播途径分为空间辐射传播和电缆传导。所以要抑制谐波,首先看看它传播的途径。电源去耦是解决传导方式传播,此外,必要的匹配和屏蔽也是需要的。

74、采用 4 层板设计的产品中,为什么有些是双面铺地的,有些不是?

铺地的作用有几个方面的考虑:1,屏蔽;2,散热;3,加固;4,PCB 工艺加工需要。所以不管几层板铺地,首先要看它的主要原因。 这里我们主要讨论高速问题,所 以 主 要 说屏蔽作用。表面铺地对 EMC有好处,但是铺铜要尽量完整,避免出现孤岛。一般如果表层器件布线较多, 很难保证铜箔完整,还会带来内层信号跨分割问题。所以建议表层器件或走线多的板子,不铺铜。

75、对于一组总线(地址,数据,命令)驱动多个(多达 4,5 个)设备(FLASH,SDRAM,其他外设...)的情况,在 PCB 布线时,采用那种方式?

布线拓扑对信号完整性的影响,主要反映在各个节点上信号到达时刻不一致,反射信号同样到达某节点的时刻不一致,所以造成信号质量恶化。一般来讲,星型拓扑结构,可以通过控制同样长的几个 stub,使信号传输和反射时延一致,达到比较好的信号质量。 在使用拓扑之间,要考虑到信号拓扑节点情况、实际工作原理和布线难度。不同的 buffer,对于信号的反射影响也不一致,所以星型拓扑并不能很好解决上述数据地址总线连接到 flash 和 sdram 的时延,进而无法确保信号的质量;另一方面,高速的信号一般在dsp 和 sdram 之间通信,flash 加载时的速率并不高,所以在高速仿真时只要确保实际高速信号有效工作的节点处的波形,而无需关注 flash 处波形;星型拓扑比较菊花链等拓扑来讲,布线难度较大,尤其大量数据地址信号都采用星型拓扑时。附图是使用Hyperlynx 仿真数据信号在DDR——DSP——FLASH 拓扑连接,和 DDR——FLASH——DSP 连接时在 150MHz 时的仿真波形。 可以看到,第二种情形,DSP 处信号质量更好,而 FLASH 处波形较差,而实际工作信号时 DSP 和 DDR 处的波形。

76、频率 30M 以上的 PCB,布线时使用自动布线还是手动布线;布线的软件功能都一样吗?

是否高速信号是依据信号上升沿而不是绝对频率或速度。自动或手动布线要看软件布线功能的支持,有些布线手工可能会优于自动布线,但有些布线,例如查分布线,总线时延补偿布线,自动布线的效果和效率会远高于手工布线。一般 PCB 基材主要由树脂和玻璃丝布混合构成,由于比例不同,介电常数和厚度都不同。一般树脂含量高的,介电常数越小,可以更薄。具体参数,可以向 PCB 生产厂家咨询。另外,随着新工艺出现,还有一些特殊材质的 PCB 板提供给诸如超厚背板或低损耗射频板需要。

77、在 PCB 设计中,通常将地线又分为保护地和信号地;电源地又分为数字地和模拟地,为什么要对地线进行划分?

划分地的目的主要是出于 EMC 的考虑,担心数字部分电源和地上的噪声会对其他信号,特别是模拟信号通过传导途径有干扰。至于信号的和保护地的划分,是因为 EMC 中 ESD 静放电的考虑,类似于我们生活中避雷针接地的作用。无论怎样分,最终的大地只有一个。只是噪声泻放途径不同而已。

78、在布时钟时,有必要两边加地线屏蔽吗?

是否加屏蔽地线要根据板上的串扰/EMI 情况来决定,而且如对屏蔽地线的处理不好,有可能反而会使情况更糟。

79、布不同频率的时钟线时有什么相应的对策?

对时钟线的布线,最好是进行信号完整性分析,制定相应的布线规则,并根据这些规则来进行布线。

80、PCB 单层板手工布线时,是放在顶层还是底层?

如果是顶层放器件,底层布线。

81、PCB 单层板手工布线时,跳线要如何表示?

跳线是 PCB 设计中特别的器件,只有两个焊盘,距离可以定长的,也可以是可变长度的。手工布线时可根据需要添加。板上会有直联机表示,料单中也会出现。

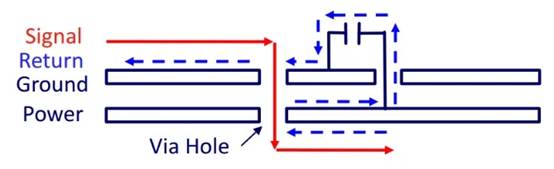

82、假设一片 4 层板,中间两层是 VCC 和 GND,走线从 top 到 bottom,从 BOTTOM SIDE 流到TOP SIDE 的回流路径是经这个信号的 VIA 还是 POWER?

过孔上信号的回流路径现在还没有一个明确的说法,一般认为回流信号会从周围最近的接地或接电源的过孔处回流。一般 EDA 工具在仿真时都把过孔当作一个固定集总参数的 RLC 网络处理,事实上是取一个最坏情况的估计。

83、“进行信号完整性分析,制定相应的布线规则,并根据这些规则来进行布线”,此句如何理解?

前仿真分析,可以得到一系列实现信号完整性的布局、布线策略。通常这些策略会转化成一些物理规则,约束 PCB 的布局和布线。通常的规则有拓扑规则,长度规则,阻抗规则,并行间距和并行长度规则等等。PCB 工具可以在这些约束下,完成布线。当然,完成的效果如何,还需要经过后仿真验证才知道。此外,Mentor 提供的 ICX 支持互联综合,一边布线,一边仿真,实现一次通过。

84、怎样选择 PCB 的软件?

选择 PCB 的软件,根据自己的需求。市面提供的高级软件很多,关键看看是否适合您设计能力,设计规模和设计约束的要求。刀快了好上手,太快会伤手。找个 EDA 厂商,请过去做个产品介绍,大家坐下来聊聊,不管买不买,都会有收获。

85、关于碎铜、浮铜的概念该怎么理解呢?

从 PCB 加工角度,一般将面积小于某个单位面积的铜箔叫碎铜,这些太小面积的铜箔会在加工时,由于蚀刻误差导致问题。从电气角度来讲,将没有合任何直流网络连结的铜箔叫浮铜,浮铜会由于周围信号影响,产生天线效应。浮铜可能会是碎铜,也可能是大面积的铜箔。

86、近端串扰和远程串扰与信号的频率和信号的上升时间是否有关系?是否会随着它们变化而变化?如果有关系,能否有公式说明它们之间的关系?

应该说侵害网络对受害网络造成的串扰与信号变化沿有关,变化越快,引起的串扰越大,(V=L*di/dt)。串扰对受害网络上数字信号的判决影响则与信号频率有关,频率越快,影响越大。

87、在 PROTEL 中如何画绑定 IC?

具体讲,在 PCB 中使用机械层画邦定图,IC 衬底衬根据 IC SPEC.决定接 vccgndfloat,用机械层 print bonding drawing 即可。

88、用 PROTEL 绘制原理图,制板时产生的网络表始终有错,无法自动产生 PCB 板,原因是什么?

可以根据原理图对生成的网络表进行手工编辑, 检查通过后即可自动布线。用 制 板 软件自动布局和布线的板面都不十分理想。网络表错误可能是没有指定原理图中组件封装;也可能是布电路板的库中没有包含指定原理图中全部组件封装。如果是单面板就不要用自动布线,双面板就可以用自动布线。也可以对电源和重要的信号线手动,其他的自动。

89、PCB 与 PCB 的连接,通常靠接插镀金或银的“手指”实现,如果“手指”与插座间接触不良怎么办?

如果是清洁问题,可用专用的电器触点清洁剂清洗,或用写字用的橡皮擦清洁 PCB。还要考虑 1、金手指是否太薄,焊盘是否和插座不吻合;2、插座是否进了松香水或杂质;3、插座的质量是否可靠。

90、如何用 powerPCB 设定 4 层板的层?

可以将层定义设为 1:no plane+ component(top route) 2:cam plane 或 split/mixed (GND) 3:cam plane 或split/mixed (power) 4:no plane+component(如果单面放组件可以定义为 no plane+route) 注意: cam plane 生成电源和地层是负片,并且不能在该层走线,而 split/mixed 生成的是正片,而且该层可以作为电源或地,也可以在该层走线(部推荐在电源层和地层走线,因为这样会破坏该层的完整性, 可能造成 EMI 的问题) 。将电源网络(如 3.3V,5V 等)在 2 层的 assign 中由左边列表添加到右边列表,这样就完成了层定义.

91、PCB 中各层的含义是什么?

Mechanical 机械层:定义整个 PCB 板的外观,即整个 PCB 板的外形结构。Keepoutlayer 禁止布线层:定义在布电气特性的铜一侧的边界。也就是说先定义了禁止布线层后,在以后的布过程中,所布的具有电气特性的线不可以超出禁止布线层的边界。Topoverlay 顶层丝印层 Bottomoverlay 底层丝印层:定义顶层和底的丝印字符,就是一般在 PCB 板上看到的组件编号和一些字符。 Toppaste 顶层焊盘层 Bottompaste 底层焊盘层:指我们可以看到的露在外面的铜铂。Topsolder 顶层阻焊层 Bottomsolder 底层阻焊层:与 toppaste 和 bottompaste 两层相反,是要盖绿油的层。Drillguide 过孔引导层: Drilldrawing 过孔钻孔层: Multiplayer 多层:指 PCB 板的所有层。

评论