基于AD9958多波形雷达信号源软硬件的设计

近年来随着雷达对抗技术的迅速发展,对雷达信号的要求也越来越高。早期的简单脉冲雷达,其发射信号波形是简单的矩形脉冲,作用距离和距离分辨率差,侦查能力差,容易被敌方截获雷达信息。线性调频和相位编码调制能获得大的作用距离和具有很高的距离分辨率,且2种编码具有不易被侦查的优点。随着近几年DDS技术的快速发展,使得线性调频及相位编码调制得以广泛应用,甚至提出了线性调频+相位编码混合编码方式。这里主要介绍利用简单脉冲技术。实现线性调频及相位编码2种调制。

2 AD9958及参数设置

AD9958是Analog Devices公司生产的一款高性能、动态特性优异、可双路输出的DDS器件,每路可单独控制频率,相位/幅度。内部集成了10 bit的输出幅度控制,内部工作频率高达500 MHz,使其可产生最高频率为250 MHz的双路信号。其内部有许多用于控制输出信号参数的控制寄存器,具有32位频率调整分辨率、14位相位失调分辨率、lO位输出幅度可缩放分辨率,有增强数据吞吐率的串行SPI口。可工作于多种模式,支持器件手册中介绍的单频信号模式(single-tone)、调制模式(moolulation mode)、线性扫频模式(1inearsweep)以及混合信号模式。

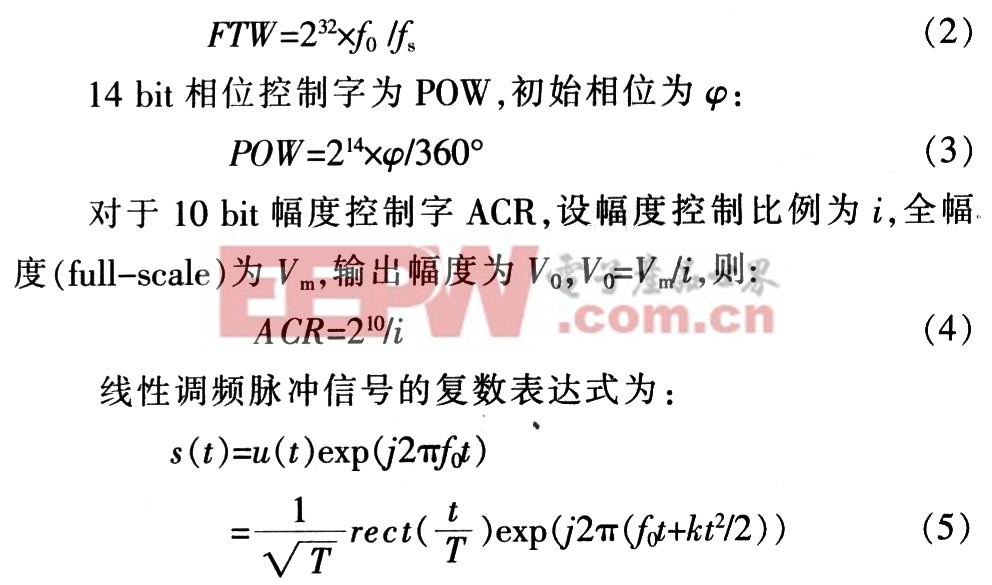

对于单频信号模式,其复数表达式为:

![]()

式中,A为信号幅度,ψ为信号初始相位,f0为信号频率。

采用这3个参数完全描述单频信号。双通道AD9958与这3个参数有关的寄存器分别为信道频率控制字(CTW0)、信道相位补偿字(CPW0)、幅度控制字(ACR)3个寄存器以及通道控制寄存器(CSR),可产生双通道正交信号,控制如下:

AD9958中需要设置初始频率、终止频率、调频斜率K确定一个线性调频信号。其中,起始频率和终止频率分别置于频率控制字寄存器CTW0和CTWl,在线性调频信号中,最主要的设置就是其调频斜率以及扫频方向,在线性扫频模式

中,频率累加器使输出频率从一个可编程低频梯变成可编程高频;或从一个可编程高频梯变成可编程低频。低频存入profile O,高频存人profile l。此时AD9958专门根据扫频方向(正/负)分别提供了上升步进频率控制字寄存器(RDW)和上升扫频时间控制字寄存器(RSRR),以及与其对应的下降步进频率控制字寄存器(FDW)和下降扫频时间控制字寄存器(FSRR),其扫频方向通过P1,P2脚单独控制,P1控制通道O,P2控制通道1,高电平表示扫频方向为正,低电平表示扫频方向为负。给出扫频方向表示为正的线性调频脉冲信号相关公式为:

式中,SYNC_CLK为系统时钟的4分频。

对于相位编码脉冲信号,在此不给出其数学表达式,只需理解其主要是对相位的选择(0相位或180相位)即可,后边将给出编码方式为巴克码和最长线性移位码的脉冲调制信号,对于AD9958,用P0一P3引脚电平控制相位选择,高电平输出相位π,低电平输出相位0。

3 系统硬件设计

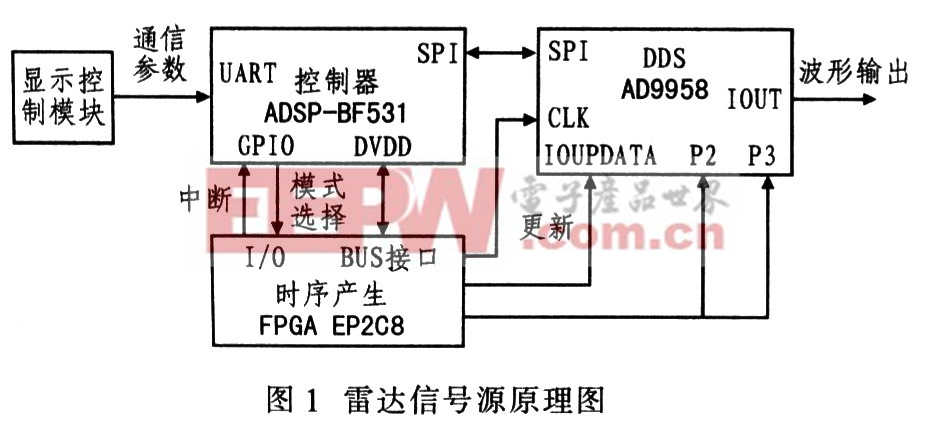

AD9958产生的雷达信号源其原理框图如图1所示。系统主要指标参数是:脉宽为5~250μs,脉冲重复周期为0.5~10 ms,带宽为1~10 MHz,可产生简单脉冲、线性调频以及相位编码调制中频雷达信号。其中对于线性调频信号调频斜率正负可选;对于相位编码,编码形式可选。

3.1 器件选型

DSP作为该系统的核心,采用ADI公司BLACKFIN系列的32位定点处理器ADSP―BF531,其最高系统时钟频率为400 MHz,BF531具有外围SPI接口和较多的可编程I/0引脚,对DDS控制有利。

FPGA部分可根据实际需要综合考虑性价比,系统选用Altera公司CycloneII系列的EP2C8。系统工作时,DSP,FPGA与AD9958 3者关系为:通信参数由前端LCD显示模块控制,通过UART送至DSP以决定系统产生波形的类型及参数。DSP中将通信参数解析计算为DDS所需的各种控制字,并通过DSP的SPI接口打入DDS内部寄存器。FPGA作为整个系统的时序控制器为DSP、DDS提供参考时钟,并接收DSP通过并行总线发送的时序控制参数,以及可编程端口(GPIO)发送的波形类控制信号,根据其中的时序控制参数(包括脉冲重复周期值和脉冲宽度值)产生DSP中断信号,以中断DSP。DSP在中断服务子程序中进行频率字的计算和发送。下面介绍FPGA作为整个系统的时序控制器时,如何产生各种时序控制信号。

评论