C波段宽带低噪声频率源的研制

摘要:介绍了利用锁相环和混频技术,实现C波段低相噪跳频源的方案,该方案通过两个环路同时实现跳频及混频,步进36 MHz,输出频率4 428~5 220 MHz,具有低相位噪声,低杂散等特点。和以往锁相频率合成的不同之处在于:以往混频时采用主环信号4 428~5 220 MHz作为混频器的RF端,而本方案为可以充分抑制辅环杂散,通过放大器将主环信号放大作为混频器的本振LO端。测试结果表明达到系统对项目的指标要求,该频率合成方案是可行的。

关键词:杂散抑制;频率合成器;低相噪;环路滤波器

微波频率源是微波通信、微波测量及雷达技术中的重要部件,其相噪性能和杂散性能直接影响到系统的性能和可靠性。因此,寻求更低相位噪声、更高纯度频谱和更高稳定度的频率源成为目前发展的主要趋势。

l 系统主要指标及方案

1.1 系统的主要指标

输出频率范围:4 428~5 220 MHz;步进频率:36 MHz;相位噪声:≤一100 dBc/

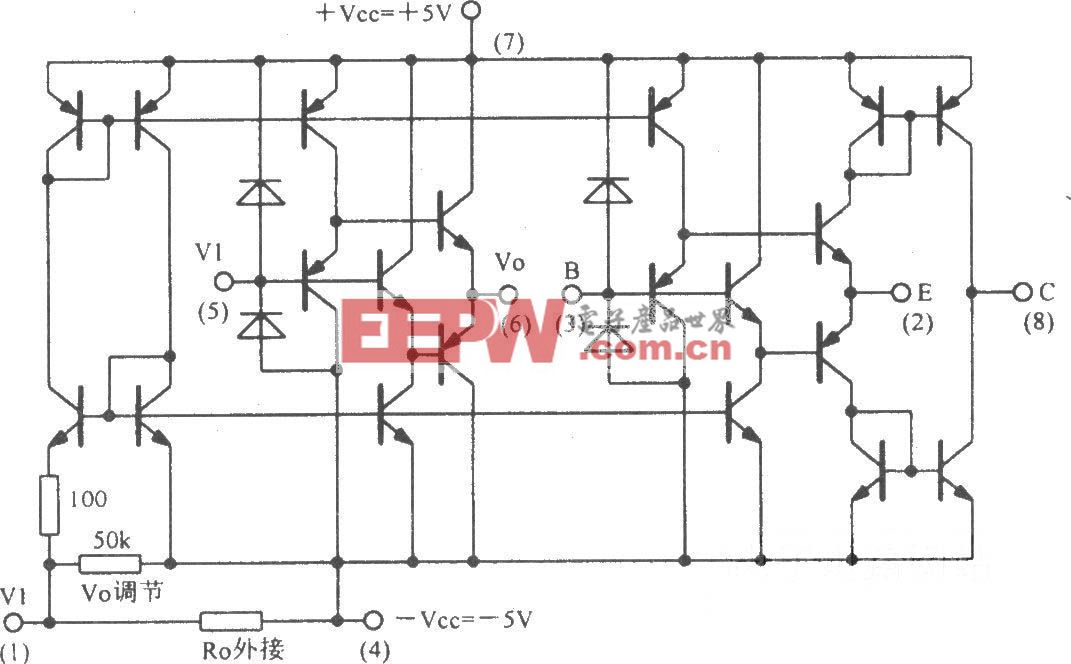

(3)由于对输出在4 000~4 200 MHz带内的杂散要求比较苛刻,而最佳辅环点频为4 140 MHz,在腔体体积一定下,很难达到一70 dBc指标,故权衡辅环相噪的恶化程度,选择4 320 MHz作为辅环。

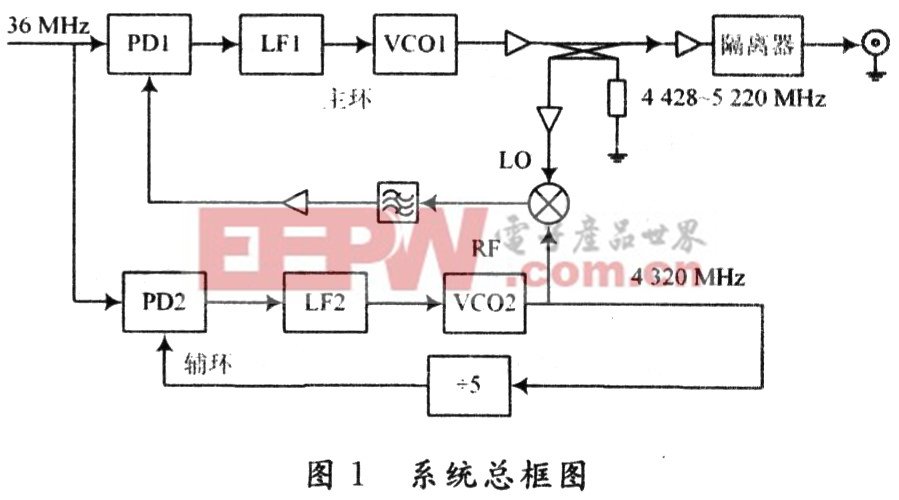

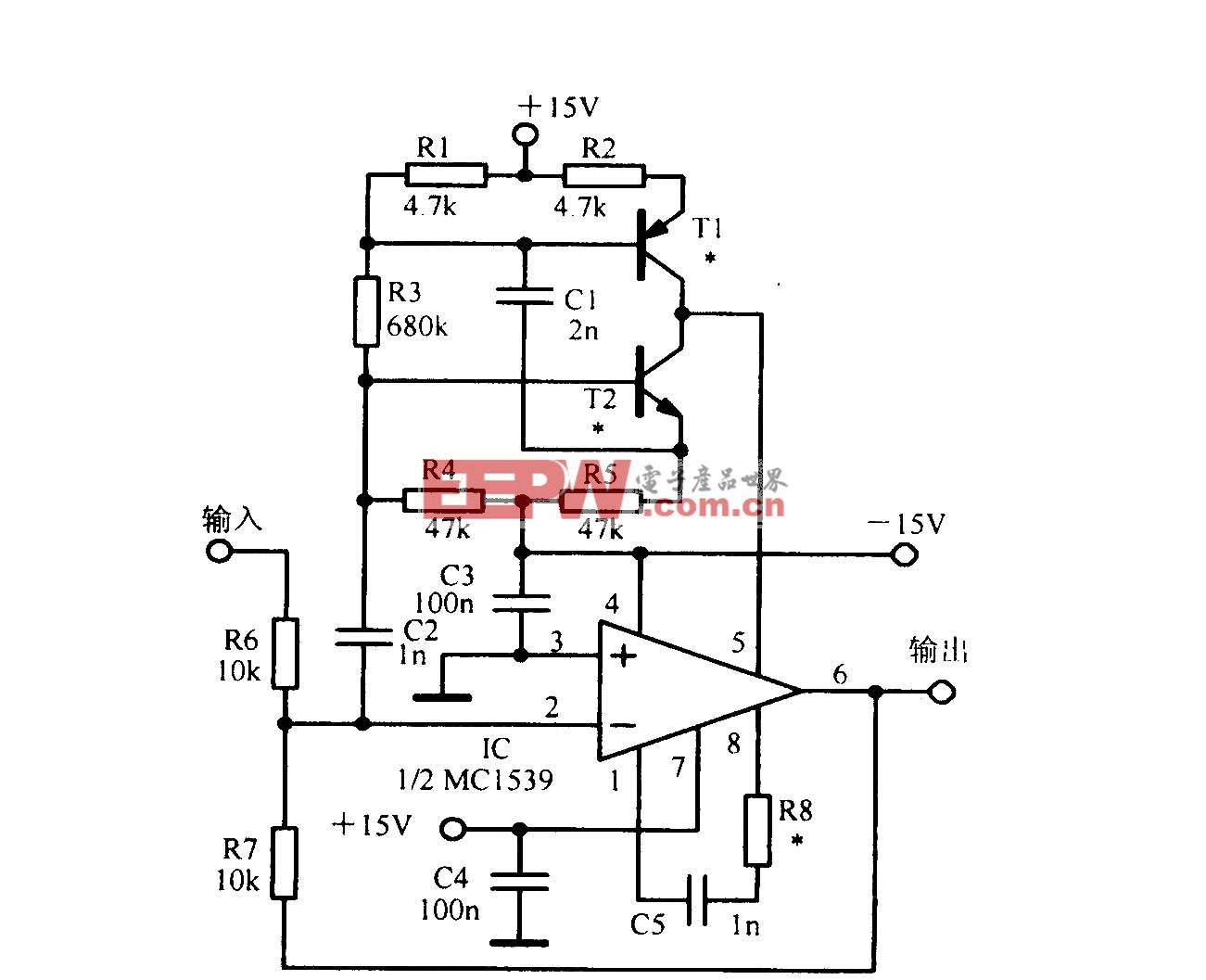

(4)为了防止辅环点频4 320 MHz作为杂散耦合到输出端,故采用功分器和将主环信号4 428~5 220 MHz通过两级放大作为混频器的本振,辅环4 320 MHz点频作为混频器的RF端。该方案选用36 MHz的低相噪恒温晶振作为两个环路的参考源,主环和辅环均选用HITTTITE公司的超低相噪模拟锁相环芯片HMC440,改善系统的相噪性能。辅环参考频率为36 MHz,输出4 320 MHz频点;主环参考频率为36 MHz,输出频率为4 428~5 220 MHz。经定向耦合器后再与辅环输出的频点混频到108~900 MHz,返回到主环鉴相器与参考频率做比较。所有的控制都由单片机来完成,根据外部数据的输入(BCD码)来进行相应的频率输出。

2 电路实现

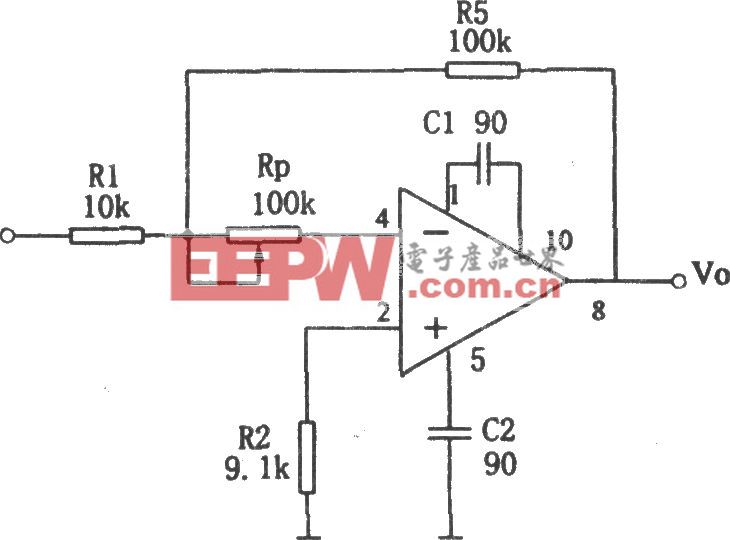

在设计单片频率合成器的时候,最主要的工作就是设计频率合成器的环路带宽,使得频率合成器指标在相位噪声、杂散、调频速度和稳定性上等方面达到兼顾,实现最佳的综合性能。

2.1 最佳环路带宽

由于本项目没有要求跳频速度,所以环路带宽采用最佳带宽设计,使得相位噪声尽可能的好。频率合成器的输出噪声如下:

![]()

式中Llp(jw)为锁相环芯片的噪声,Lvco(jw)为VCO的相位噪声,Hn(jw)是被N规一化的环路滤波器的传递函数。由上式可以看出环路对带内噪声源呈低通过滤,故希望将环路带宽fc越低越好;但环路对VCO呈高通过滤,又希望环路越宽越好。为了兼顾这一对矛盾,参考图2能够使两种相位噪声都得到合理的抑制,可以选择环路带宽fc在两噪声源谱密度线的交叉点附近总是比较接近于最佳状态的。但是考虑晶振噪声要恶化20log(N/R),所以实际带宽要略小一些。

评论