快速而准确的数千兆赫兹级串行收发器建模技术

利用仿真手段验证串行链路信道是非常重要的。在非理想信道中,仿真需要包含成千上万个位的变化。工程师可以通过下载MacroModel模板,根据要求进行必要的修改后,依赖各种资源和本文提到的实例,可创建更快速的模型来执行这种类型的仿真。

本文引用地址:https://www.eepw.com.cn/article/188600.htm随着差分信号频率的不断提高,数千兆赫兹级(MGH,Multi-GigaHertz)系统仿真已势在必行。特别是当系统和封装的探测变得越来越困难,硅片中的信号越来越明显地需要均衡嵌入时更是如此。而硅片封装电路板建模技术还在十字路口徘徊;IBIS模型不能处理预加重,晶体管模型速度太慢,无法仿真足够的位数。这样的问题影响到了你的设计吗?

用于MGH仿真的新技术已经推出,这种技术也许要比想象中的更简单。本文将说明这种解决方案的重要性,并解释应用时需要知道的一些基础理论。经过深入研究后你会发现后续步骤只是简单的点击鼠标而已。

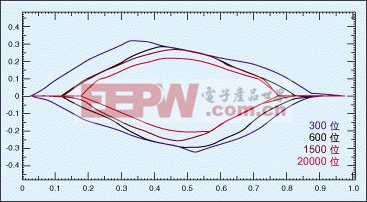

拓展眼图,仿真更多的位数 ALT=图1:仿真位越多,眼图高度越小。>

ALT=图1:仿真位越多,眼图高度越小。>

串行MGH收发器主要用来适配并作用于多种多样的系统互连或“信道”中间。而这些信道通常都很不理想,具有各种各样的损耗以及不连续和不匹配的阻抗特性。快速仿真一般都能发现这些问题,并帮助找到解决方案,同时也可用来证实差分信号电压能按要求进行切换。

然而,非理想信道也可能会产生一些令人难以理解和量化的行为。某些位模可能会结合系统中未端接的能量而产生不可预期的结果。虽然象8b/10b这样的编码方法能够减少可能的位组合数量,但如果没有测试长位流的话很难对信道做到完全验证。这里的“长”正比于被信道的恢复时间或“存储器”覆盖时希望的位变量。

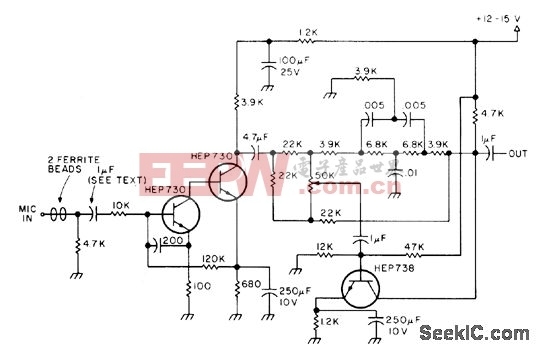

如图1所示,我们需要对信道进行长位流验证。从图1可以看出,当仿真的位数量增加时,MGH串行链路的眼图高度会变小。与300位时的测试相比,在测试20,000位后眼图高度减少到了60%。事实上在信道收敛性能测试之前,非理想信道的眼图高度在最开始的100,000位测试中会很快下降。这种巨大的变化会给正常的系统设计带来很大的隐患。

对更快模型的需求

为了理解更长位流情况下信道的行为,必须找到仿真速度更快的硅片模型。虽然晶体管级模型具有很好的精度,但即使是仿真几百个位也需要很长的时间。用每小时完成100位仿真的典型晶体管级模型来仿真百万位数据则需要花上一年多的时间,显然这是不能接受的。

为了应对这一挑战,Cadence公司提供了可下载的“MacroModel”模板,设计师可以用它快速生成自己的MGH器件模型。由于这些模型得到了优化和行为化,一般仿真速度能比晶体管模型快数百倍。采用这类模型后能够轻易实现长位流的仿真,因而也能完成更好的信道验证。

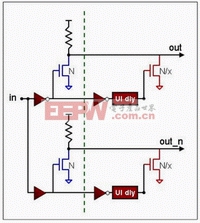

理解预加重 ALT=图2:预加重发送器和模型的基本结构。>

ALT=图2:预加重发送器和模型的基本结构。>

本文最后会告知如何取得这些模型模板,但首先来了解一些高效使用这些模板的基本知识。

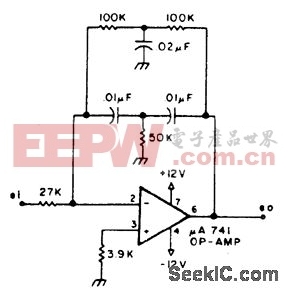

大部分1到5GHz范围内的MGH收发器使用2节点的“预加重”。可能许多设计师都很熟悉这个术语,却并不清楚它是如何实现的,也不知道如何给它建模。然而“预加重”这一特点会使这些发送器在行为级IBIS模型结构中不能正常工作。为了继续这一讨论,本文假设读者了解IBIS模型中的基本单元,但想知道带预加重的发送器有什么不同。

图2给出了差分发送器中的基本单元。虚线左边的每个器件可以用IBIS处理,人们也比较熟悉。信号被驱动成高电平,并端接于电阻,同时使用尺寸为N型并连接到地的蓝色晶体管驱动到低电平。虚线右边的预加重单元增加了一个反向器、一个单位时间间隔延迟“UI dly”和另外一个晶体管。这个附加的红色晶体管是蓝色晶体管的缩减版本,尺寸为N/x,以并联方式连接。

评论