实用I/O地址译码电路设计

0 引言

PC机的软件资源十分丰富,而工控PC机的应用更是日益广泛。为了达到与外部相联系的目的,通常都会制做A/D、D/A等具有特定功能的卡,然后直接插入PC机主板的扩展槽上,而且每个卡都有自己的I/O地址。PC机器I/O地址范围为000~3FFH,其中系统板和计算机外设占用了一部分,给用户保留了一部分。但用户地址译码要在卡上实现,并且要避免与其它卡的地址冲突,它的地址应能用跳线或其它方法进行改变。

1 基于8位比较器的译码电路

该译码电路的核心器件为8位比较器74LS688,图l所示是其电路图,其中,SW为8位拨段开关,通过改变其开关位置,可以达到改变I/O地址的目的。74LS688比较器的功能见表1所列。当Pi=Qi(i=0,l,2…7)时,输出有效。参与译码的地址线为A0~A9,其中与比较器相连的地址线为A2~A9,而A0一A1则留作卡上芯片的内部寻址。该译码电路的I/O地址选择范围较宽,为000H~3FFH。Pi和Qi的排列没有按顺序排的主要原因是考虑到PCB图的布线美观、方便(与比较器引脚有关)。AEN是PC总线的一个输出信号。表1中的高电平表示计算机处于DMA响应周期,这时要禁止I/O地址译码。

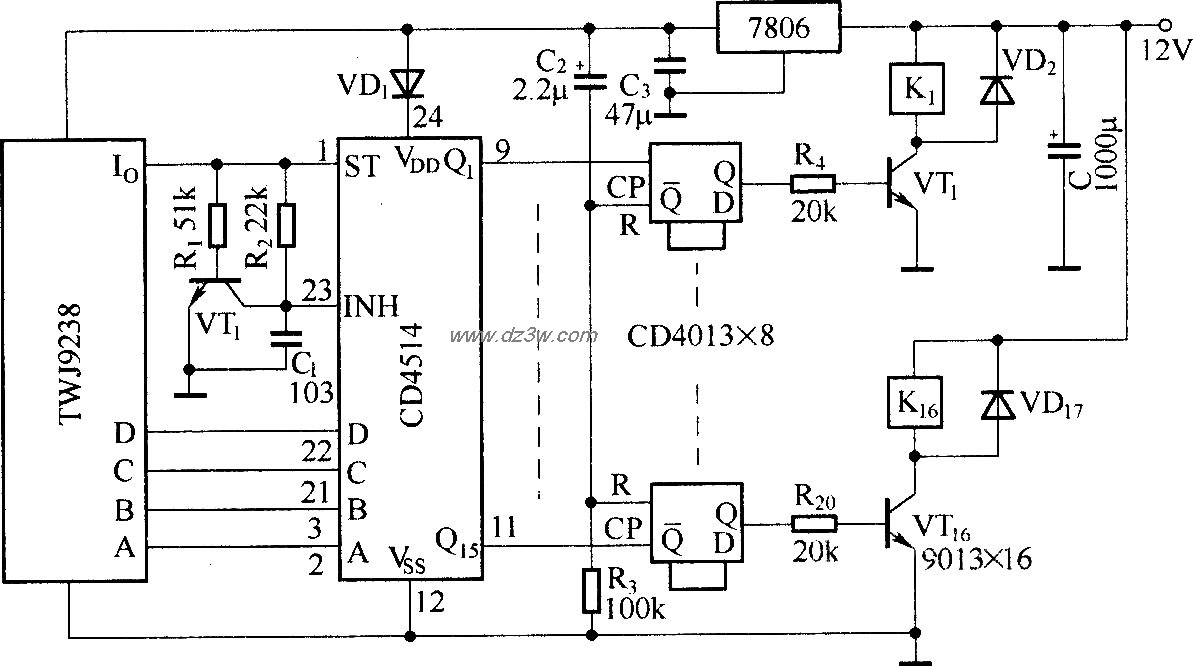

2 使用局部译码的译码电路

使用局部译码的译码电路其原理图见图2所示。该电路的特点是有8路译码输出,并可通过改变跳线S1、S2、S3来改变I/O的地址范围。设跳线S1、S2、S3向上短接和非门的输出相连时,状态为“0”,而向下短接和非门输入相连时,状态为“1”,那么,会出现如

评论