单芯片极窄微弱脉冲检测系统设计

摘要:采用O.18 μm CMOS工艺设计了一款单芯片集成极窄微弱脉冲检测系统,该芯片包括输入匹配、放大器、脉冲展宽器、驱动及带隙基准电压电流产生电路。为提高检测系统灵敏度,文章采用了多级放大器级联以及有源电感。测试表明该芯片可以检测1ns脉宽10mV的脉冲,输出数字信号,可以应用于00K系统接收机,接收超过40M数据率的清晰视频。该芯片低功耗、低成本,具有研究和实践推广价值。

关键词:脉冲;检测;放大器;有源电感

0 引言

随着大规模集成电路的发展,单芯片方案由于成本低、体积小、功耗低等优点,被越来越多的电子系统所采用。

微弱脉冲信号检测和识别在通信、医疗中都有广泛应用,将微弱脉冲信号检测系统单芯片化具有现实的研究意义。

1 微弱脉冲检测系统框架设计

本系统的设计目标是用低成本CMOS工艺实现1ns、10mV脉冲信号的检测,并输出FPGA可处理的数字信号,用于超宽带无线通信OOK接收通道,见图l。

对于纳秒级信号的检测,传统接收机方案采用需要高速时钟的高速ADC来实现模数转换,高速时钟产生电路一般应用频率综合器方案,消耗较大面积和功耗,且同样需要外接参考时钟。

高速ADC使用时钟的重要原因之一是为了利用正反馈来弥补放大器在高频情况下的增益不足。随着集成电路工艺的进步,器件寄生电容越来越小,0.18μm CMOS工艺截止频率已达40GHz,通过使用有源电感,已可以在较低功耗下实现较高的高频增益。

本系统要求单片集成,低成本、低功耗,采用多级放大器级联的方案来提高检测系统的分辨率,并对输出信号通过延时电路来加大脉宽,降低后续基带部分数字信号处理电路的压力。

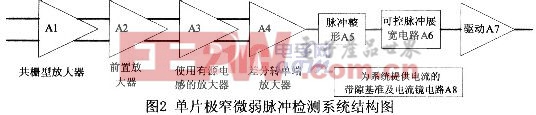

本系统具体框架见图2所示。前一级是片外的检波器,通过50Ω微带线将信号输入,所以本系统需要将输入阻抗匹配为50Ω。本系统第一级为共栅型放大器,主要为系统实现输入匹配,并提供一定的增益。第二级为一个4输入放大器,可外置阈值电平。第三级为一个高频放大

器,使用了有源电感,可以在较低功耗下达到较高的带宽。第四级为差分转单端放大器,将差分信号转为单端,并提供一定的增益。第五级为一对反相器,提供非线性增益,将信号整形为数字信号。第六级为可控脉冲展宽电路,将1ns脉冲展宽为5ns。最后一级为反相器阵列组成的驱动,可以驱动5pF电容和50Ω电阻。本系统同时集成了为核心电路提供电流的带隙基准电路。

评论