高速高精度钟控比较器的设计

在现代通信和信号处理系统中,高性能A/D转换器作为连接模拟和数字世界的重要通道被广泛应用于医学图像、高速数据变换及QAM调制器等重要设计领域。比较器是模数转换器设计的核心单元,其精度、速度、失调电压和回馈噪声等因素直接影响着系统模块的整体性能。传统的预放大锁存比较器通过采用3级或3级以上级联的预放大器结构降低比较器的传输延时和回馈噪声,但这些指标是以较高的功耗和增加芯片面积为代价的。典型的A-B型动态锁存比较器具有高速、低功耗的特点,但该结构存在着较大的回馈噪声和失调电压,限制了比较器精度的提高。综合考虑以上因素,基于TSMC 0.18μm CMOS标准工艺,本文设计了一种可应用于高速高精度A/D转换器的比较器结构,给出了提高比较速度和降低回馈噪声的理论和方法,并基于此进行了电路的设计与优化。

1 比较器电路设计

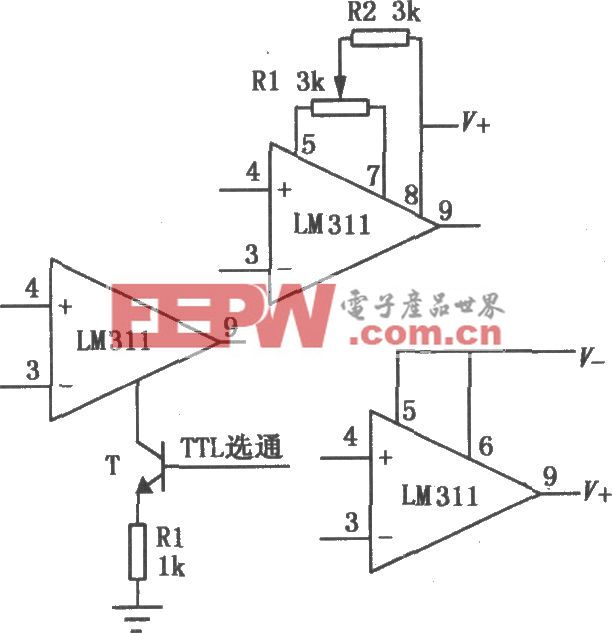

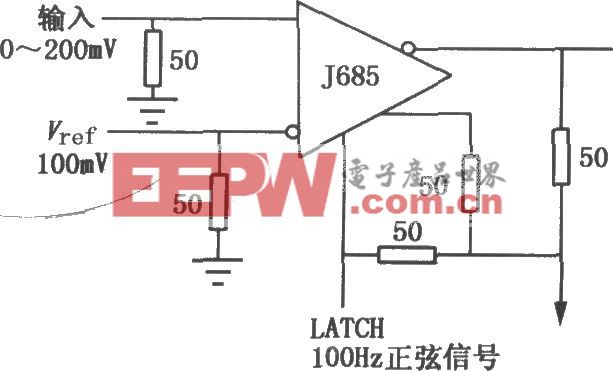

本文设计的高速高精度钟控比较器从功能上可划分为3级,包括预放大级,钟控比较级,输出缓冲级,如图1所示。输入信号通过预放大级电路放大,并由时钟信号控制把放大后的信号传输到钟控比较级进行再生比较,最后利用正反馈结构的输出缓冲级电路将输出电压迅速转化成逻辑电平。

1.1 预放大级

为了满足高速、高精度的要求,预放大器的设计原则是高带宽低增益。单纯的以MOS二极管和电流源为负载的放大器具有有限的增益带宽积,不能同时兼顾速度和精度的要求,使用二极管和电流源负载的混合结构可以满足良好的增益和带宽的折衷。

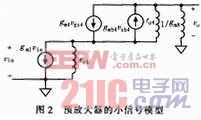

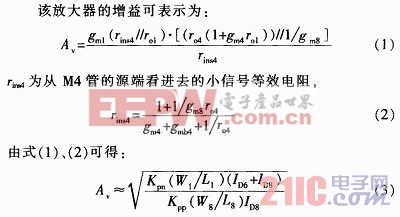

针对图l中预放大级,VM1、VM2构成差分放大管,二极管方式连接的MOS管VM8,VM9为差分对的有源负载,增加PMOS镜像电流源VM6、VM7的目的是使输入晶体管偏置电流的一部分由PMOS电流源提供,这样可以通过减小电流而不是减小宽长比来降低负载管的跨导,进而提高差动增益。VM4、VM5为钟控开关晶体管,当时钟信号clk为高电平时,其与输入差分对构成共源共栅结构,提高电路对输入信号的放大能力;当时钟信号clk为低电平时,其可以有效隔离输入信号与再生节点馈通的回馈噪声,这对保证电路的性能非常重要,预放大电路的小信号模型如图2所示。

从式(3)可以看出,通过合理调节管子的宽长比和电流源注入的电流值可调节放大器的增益和频率特性。需要注意的是,为同时满足高速比较器对响应时间的要求,设计中在保证增益的同时尽量增加预放大器的带宽。该预放大器的增益、带宽仿真结果如图3所示,增益为18.352 dB,-3 dB带宽为1.122 GHz。

评论