使用序列门控在扫描位移中实现强大的时序闭合

如今,所有SOC都使用扫描结构来检测设计中的任何制造缺陷。扫描链专为测试而设计,按串行形式连接芯片的时序元件。由于扫描元件之间缺少组合逻辑,因此这些扫描链容易出现保持故障。除了采用小于90纳米的技术外,OCV(片上工艺偏差)对时序裕量有着巨大的影响。因此,除非设计在多个拐角处实现时序签核(sign-off),否则极有可能出现保持故障,尤其是在扫描链等保持关键路径上。这些保持故障会导致芯片无法在实际的应用中使用(即便芯片能够在功能场景中完全运行也会如此)。如果芯片中出现这些故障,将会降低成品率,影响产量,由此导致设计公司蒙受巨大的经济损失。因此,我们需要设计一个强大的扫描结构来解决上述问题。

本文引用地址:https://www.eepw.com.cn/article/187486.htm在本文中,我们将首先快速回顾锁存器与触发器的时序基本概念。在下一节中,我们将介绍扫描链以及与其相关的时序闭合问题。然后,我们将解释如何在扫描链中使用锁存器和触发器创建强大的扫描结构,以避免在小于90纳米的技术中出现时序故障。我们将介绍最优秀的解决方案,满足扫描链中所有可能出现的时序元件组合的时序要求。

建立/保持时序概述

触发器和锁存器是时序电路的两个基本构件。触发器在所应用的时钟脉冲的活动边沿(正或负)更改其状态。触发器在无活动时钟边沿时只保持其输出。另一方面,锁存器是电平敏感器件,它不断对其输入进行采样,并相应地在某些电平启动信号的活动脉冲电平(正或负)上更改其输出。触发器采用主从配置,有两个锁存器在彼此相对的活动电平上以级联方式工作。一个触发器的面积几乎是锁存器面积的两倍。

为了实现同步设计,我们需要确保触发器/锁存器的输出不处于亚稳状态。这可以通过在设计中满足建立和保持检查要求来确保。

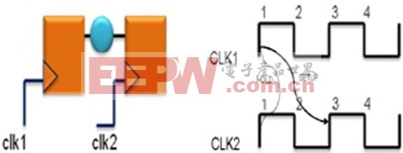

图1

在触发器中,1-1是保持检查,而1-3是用于单周期操作的建立检查(图1)。我们需要确保由触发器1发出的数据在下一个活动边沿之前由触发器2捕获。同时,我们也需要确保由触发器1发出的数据在相同的活动边沿上没有被触发器2捕获。

图2

当第二个触发器被负边沿触发后,建立检查将是1-2(见图2),而保持检查将发生在上一个负边沿(见图2)。这意味着由触发器1发出的数据不应被之前触发器2的下降沿捕获。除非我们拥有超过半个周期的时钟偏移,否则无法以实时的方式将其实现。

因此,在正-正或负-负触发器对中,建立检查默认为一个周期,保持检查为零周期,而在正-负或负-正触发器对中,建立检查默认为半个周期,而保持检查为反向的半个周期。现在让我们了解一下锁存器中的时序检查概念。

扫描链

扫描链用于在SOC中执行测试。设计中的所有寄存器以串行形式连接,外部芯片提供刺激,然后读出这些链的输出,监测是否有固住/状态转换故障。当今的SOC都非常复杂,并且在单一芯片中具有多个时钟域。虽然在逻辑合成之后扫描会拼接出一个设计,一般还是需要注意将具有相同时钟结构的触发器拼接在同一个扫描链中。但是,由于可用于最高级别的扫描输入/输出端口是有限的,因此在不同时钟域之间混合寄存器是无法避免的。使扫描链具有不平衡的长度也不是最佳解决方案,因为这样会增加总体测试时间。因此,这种设计结构会在之后的设计阶段中导致时序闭合问题。因为扫描位移在低频进行,并且触发器对,之间需要的逻辑最小,如果有的话,因此建立闭合将不是问题。但是,因为最小逻辑和触发器对之间出现的偏移,这些路径是关键的保持路径。正如我们在前面所讨论的,因为来自不同域中的触发器在扫描链中被混合,所以在许多情况下发出和捕获触发器之间会出现巨大的偏移。在设计的后期阶段,由于噪声的影响会出现许多保持时间违规,这将导致无论在稳定或闭合设计中都会出现保持缓冲,从而引发设计故障。

更差的情况可能是,我们的减额裕量可能并不充足,并且我们仅可以从硅片上发现保持故障。如果异常的时钟路径非常巨大,并且硅片上的实际偏差高于预计偏差,则有可能会出现这种情况。当我们进一步使用小于90纳米的CMOS技术时,偏差影响将变得越来越占主导地位,并将导致硅片上出现许多保持偏差。扫描移位路径中的保持故障会导致严重的后果。需要进行多次调试,并且需要花许多时间来检测硅片上的故障链。当我们也具有用于扫描的压缩逻辑时,这种情况会变得更加糟糕。即使检测到了故障链,我们也需要将其阻塞,这将导致减少测试覆盖范围。

总之,扫描链中的保持故障风险很高,必须实现足够强大的设计才能处理这些不确定因素。

可以有多种解决方法,例如,对扫描链重新排序,根据寄存器的位置重新布置扫描链。尽管这些技术非常容易获得,设计者也必须对其进行仔细探究,正如我们前面所讨论的,扫描链在两个时钟域之间交叉的情况是不可避免的。

解决这种问题的一种更为有效的方式是提前采取措施,并在构建扫描链的逻辑合成阶段处理这些问题。来自相同时钟门控逻辑的所有触发器都应拼接在一起,并且在这些触发器束的末端可以插入一个锁定的锁存器,以避免从这个域的最后一个触发器到下一个时钟域的第一个触发器之间出现任何保持故障。

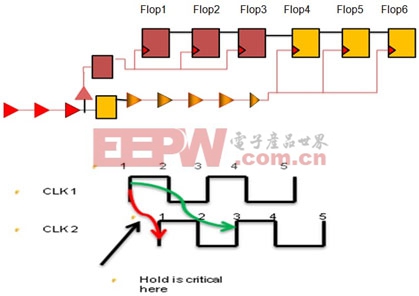

图3所示的例子将有助于我们理解这一概念。

图3

如果时钟周期为50ns并且偏移为5ns,我们必须在设计后续阶段的触发器3和触发器4之间插入具有相当于5ns以上减额裕量的保持缓冲器。正如前面所讨论的,由于小于90纳米设计中的ocv,我们的标准减额可能因为异常时钟路径超出特定限制而变得并不充足。例如,对于具有10个额外时钟缓冲器的捕获路径来说,每个时钟缓冲器只具有5ps偏差(超出并超过减额值)将导致50ps的偏离。另外,由于OCV的因素。这一偏移可能会超过5ns,该一裕量可能并不充足。

解决上述问题的解决方案是在触发器3输出中插入锁定的锁存器,同时使锁定的锁存器具有与触发器3相同的延迟。

lockup latch:锁定锁存器;clock gating:门控

zero cycle check hold, easy to meet: 零周期检查保持,易于满足;

shifting of data from flop 3 to 4 is still in one shift cycle:从触发器3到触发器4的数据转移仍然保持在一个周期内。

Hold check is half cycle back now, much relaxed now: 保持检查现在只占后半个周期,比以前轻松很多

图4

正如以上波形中所示(图4),当我们在 触发器3 和触发器4之间插入锁定锁存器时,我们的时序路径将被分为两个阶段。

1. 从触发器3到锁定锁存器

保持检查从1-1开始,它仍然是零周期检查,但是因为没有偏移,因此非常简单易行。默认建立检查从1-2开始。

2. 从锁定锁存器到触发器4

保持检查从2-1开始。这是插入锁定锁存器的主要优势和动机。保持是向后移位半周期,现在即使我们的时钟偏移高达半个移位时钟周期,我们仍具有足够的裕量。这可以确保在这种情况下不会出现任何保持偏差。

建立检查从2-3开始。在2-3期间锁存器是透明的,这一阶段中捕获的任何数据都将被传输至触发器4,直到边沿 3(减去触发器的建立时间)。我们可以看到,从触发器1到锁定锁存器之间的建立检查也可以轻松完成。1-2是默认检查,但是锁存器在整个半个周期的过程中都是透明的,在理想情况下,建立检查可以向边沿3位移。(这一概念被称为锁存器借用)。

此处,另外一个需要注意的重要事项是该锁定锁存器应具有与发出触发器时钟相同的时钟,而不是与捕获触发器时钟相同。正如我们在上面所看到的,触发器3到锁存器的保持检查仍然是1-1(零周期检查)。如果锁定锁存器具有与捕获 触发器时钟相同的时钟,我们将不会得到任何优点。因此,理想的解决方案是在时钟树结构中发出触发器和锁定锁存器都由相同的时钟缓冲器驱动。

以上示例说明,锁存器可以在扫描移位路径中有效地混合保持。也许有人会提出疑问,我们是否也可以通过插入保持缓冲器或延迟cell来修复这些偏离。但是,快速查看保持缓冲器的面积,延迟cell和锁存器表明,保持缓冲器适合用于混合较小的保持偏离,但是如果偏离较大,则锁存器在面积和延迟方面都比缓冲器更有优势。使用延迟cell时,不同操作条件之间始终存在巨大的偏离风险,因此应当有选择地、巧妙地使用这些cell。在另一方面,锁存器在任何操作条件下始终存在半个周期的延迟。

在最后一节中,我们将考虑各种情况,找出在扫描链的发出和捕获触发器之间出现巨大的时钟偏移时修复保持故障的最适合的解决方案。

不同情形

情形1:正-正边沿触发触发器之间

我们在以上示例中包括了这一情况,可以使用负电平锁存器。

情形2:负-负边沿触发触发器之间

通过上述相同的模拟,可以使用正电平锁存器。

情形3:负-正边沿触发触发器之间

我们已经了解到保持在此处非常轻松。此处不需要锁定元件。

情形4:正-负边沿触发触发器之间

这是一个非常有趣的情形。从时序的角度来看,这种情况不会造成问题,但是在扫描移位中这是一个非法连接。由于在ATPG中,时钟被视为返回至零波形(在移位完成后,时钟将变为活动低电平),如果我们允许这种交叉,我们将发现在扫描移位后,所有此类的正-负对在时钟脉冲后将具有相同的值。因为所有触发器都不是可以独立控制的,因此这将导致测试覆盖范围减少。在拼接时应该避免出现这种情况,但是有时候无法避免,因为存在压缩逻辑或硬宏。

我们可以在正和负触发器之间插入一个正电平锁定锁存器,这样将解决ATPG问题,但是同时也会带来时序问题,因为保持检查在从触发器到锁定锁存器以及从锁存器到负边沿触发器之间将再次变为零周期检查。

另一个解决方案将插入一个哑触发器,可以在这些触发器之间的正边沿或负边沿上工作。应该注意的是,在移位后哑触发器将仍然具有与第一个触发器或第二个触发器相同的值,这取决于它是在正边沿触发还是在负边沿触发,但这不会导致任何问题出现,因此它不是一种功能性触发器,我们不会以任何方式在任何位置使用它来捕获数据。如果我们决定插入正边沿触发器,发出 触发器的时钟延迟和该dummy 触发器将相同,因为它将是零周期保持检查,并且哑触发器到下一个触发器将是半周期保持检查,同样,如果我们插入哑负边沿触发器,捕获触发器和哑负边沿触发器的延迟是相同的。

这些就是设计中可能存在的触发器之间的所有四种情况,但有时候这些情况并不十分明显。例如,在扫描具有硬宏且是预拼接的设计时需要特别注意。许多情况下我们并不具备针对硬宏的netlist/spef/timing约束,因此我们建议在这些硬宏之前插入锁定锁存器,以防这些硬宏的所有者将其丢失。另外一个此类示例是burn-in模式,设计中的扫描链将被连接在一起,以便同时切换所有触发器。因此同样存在这种可能性,也就是说链中的最后一个元件和下一个链的第一个元件具有时序关键逻辑或无效的正-负交叉。对于此种情形,理想的情况下应该注意RTL本身,因为设计者在将这些扫描链连接在一起能够更好地了解扫描元件的顺序。如果未将其考虑在内,最佳的做法是在每个链的结尾处插入相应的锁定锁存器。

通过采用上述技巧和指导,设计者可以在其芯片上实现强大的扫描结构。在出现建立故障的情况下,设计可以在更低的频率上运行,但是在出现任何重大保持故障时,逻辑的既定功能是无法预测的。扫描位移中的保持故障非常严重。它会在测试期间极大地缩小测试覆盖范围。因此,我们需要一个强大的扫描结构,解决我们前面所讨论的潜在的扫描移位故障问题。相应的锁定类型元件可以完美地解决此类问题,因为它可以在任何操作条件下确保半个周期的延迟。

评论