中频数字化正交解调结构介绍

传统的中频数字化正交解调系统中芯片选择的限制及成本的大幅上升。为此提出了一种新的中频数字化正交解调系统结构,在保留高速A/D的高数据率输出的同时,大幅降低现场可编程门阵列工作频率,并进行了仿真,验证了系统结构的可行性。

本文引用地址:https://www.eepw.com.cn/article/187263.htm1 数字正交解调原理

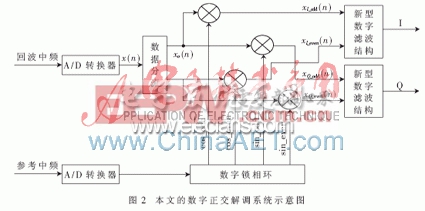

数字正交解调结构如图1所示,参考和回波中频模拟信号经由2个A/D转换器同步采样量化,然后把数据送入现场可编程门阵列(FPGA)中实现数字下变频。在FPGA中,将参考中频的采样结果输入数字锁相环进行锁相之后,产生2路正交的数字中频载波信号。分别与回波中频信号的采样结果相乘,实现频域的搬移。再分别进行数字滤波得到I、Q 2路正交数字基带信号后,将数据输出至后端数据处理单元。

2 数据正交解调系统设计

图2所示为本文提出的中频正交解调结构框图,针对高速A/D转换器数据率大的特点,在FPGA内部,通过DEMUX将回波中频采样数据x(n)拆分为奇序列xo(n)和偶序列xe(n),分别进行处理,使数据速率降为原先的一半。同时,为了使载波序列与X(n)拆分后序列正确匹配相乘,数字锁相环输出调整为2组4路载波信号: cos_odd与sin_odd、cos_even与sin_even与相应的回波拆分序列相乘。得到4路混频信号xl_odd(n)与xl_even(n), xQ_odd(n)与xQ_even(n)输入数字滤波器。

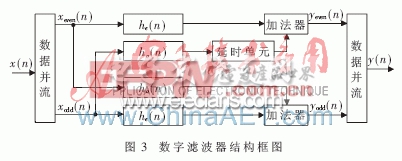

由式(3)、式(5)可得一种新的数字滤波器结构形式(见图3),其特点在于将数字信号序列拆分为2路,同时将滤波器系数拆分成2个子滤波器,通过2个子滤波器对2路拆分信号的滤波输出组合得到对原数字信号序列滤波输出的奇数项和偶数项。经过上述处理,子滤波器的工作频率可降为原滤波器频率的一半,因此在具体实现时可获得比原滤波器更高的工作频率,这样合成滤波器的工作频率可达到原滤波器工作频率的2倍以上。

最后将2组混频输出信号xl_odd(n)与xl_even(n),xQ_odd(n)与xQ_even(n)分别通过2个数字滤波器后,就可以得到解调后的正交基带信号I,Q。

评论