高整合USB微控制器简化嵌入式系统连结设计

USB连结是许多嵌入式应用的重要规格;高度整合的USB微控制器解决方案,不仅能以最简易的方式为嵌入式系统建立USB连结,还能提供高效能的CPU功能;其所附带的整合式类比周边更有助于降低元件数量和材料清单成本,进一步满足市场需求。

本文引用地址:https://www.eepw.com.cn/article/187069.htm

高整合度USB微控制器可以高成本效益,完成嵌入式连结功能设计。

加入更多功能/周边降低整体成本

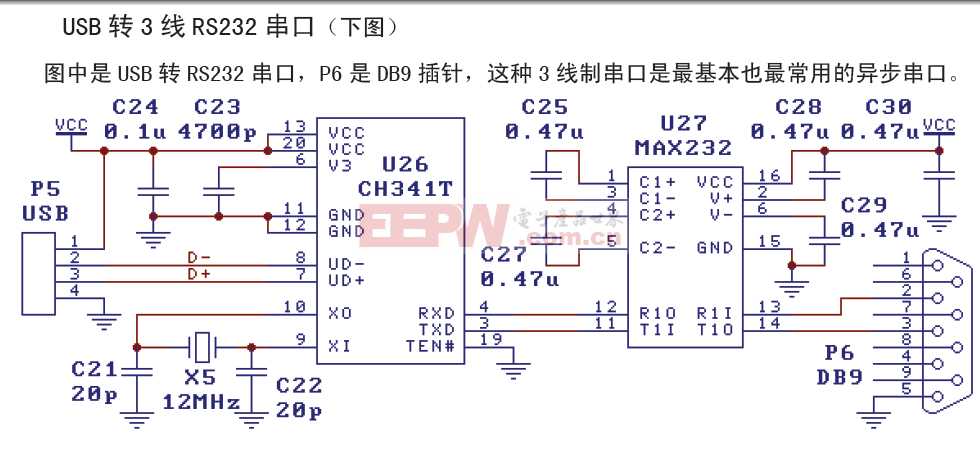

USB在工业和消费应用中迅速获得采用,同时也为嵌入式解决方案的设计人员带来挑战,因为设计人员须把USB连结融入产品中,且还要维持或者降低整体成本。早期版本的USB微控制器是为增设USB介面所开发,但它没有能力支援其他的功能或周边设备。当USB刚推出时,这些元件在推动USB介面的全面普及上扮演重要的角色,即使到今天,这些桥接元件也可当作有效解决方案。只要透过辅助晶片,即可迅速增添全速型USB,而不必重新设计整个系统。不过,对于一些成本敏感的应用,这种做法或许不尽理想。

为克服成本上的难题,新一代的USB微控制器加入更多的功能与周边装置。不过,具备不同周边功能的USB微控制器虽然在市场上大幅成长,但还是不及高度整合的解决方案。高整合度的USB解决方案不仅能加入适当组合的周边装置,还能确保这些功能强大到足以支援重要的应用需求。虽然应用需求深受终端产品的特性与功能所影响,但大部分的应用主要须涵盖三个共通的层面。

首先是中央处理器(CPU)的效能以及把USB并入周边装置的影响;第二须考量的层面是,在类比功能或周边装置上扮演真实世界讯号连结的要角;最后,由于各种应用对成本几乎都很敏感,因此可消除外部元件需求以降低成本的USB建置便十分理想。

CPU主要的功能为执行用户码,所以它能不能及时执行指令并处理资料便至关重要。一般符合成本效益的USB控制器都会采用先进先出(FIFO)的方式来管理进出的封包,而CPU可将资料存取于缓冲器内,并同时执行其他的作业。

CPU/USB功能交互作用难题迎刃解

在桥接应用的例子中,假设需求是要把序列式的通用异步收发器(UART)桥接到USB的系统上。最简单的方法,CPU应该要能从UART介面撷取资料,并存入USB FIFO中,反之亦然。不过,要是同样此应用须执行其他简单的功能,像是反转字节排序,或者执行复杂的功能,如套用软体过滤程式,该怎么办?一开始的简单作业突然变成极为复杂的运算,而这须要经过特别的处理才能妥善管理,于是对CPU所造成的负担便愈来愈大。

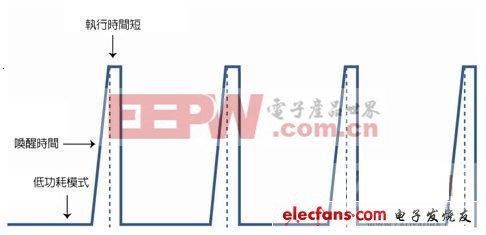

一般的协定桥接都是把一个周边装置的资料传往另一个,并且几近即时,所以CPU须具备必要的效能来读写及运作资料,延迟时间也要缩短到能让人接受。芯科实验室(Silicon Labs)推出一系列的微控制器,为低价USB解决方案中较佳的范例,该系列微控制器具备强化的高速CPU,能够在一或二个系统时脉周期就能执行七成的指令。这种效能不仅足以满足协定桥接应用的需求,还能支援其他大部分的高速USB应用。另一个优点是,高速CPU能在较短的时间内执行较多的工作,所以能降低整体的耗电量,并使系统在低功耗模式中维持较长时间运作(图1)。

图1 高效能微控制器可使系统在低功耗模式下延长作业时间

评论