关于不同类型的时钟讨论

无论是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为,并且调试困难、花销很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

本文引用地址:https://www.eepw.com.cn/article/186413.htm1.全局时钟

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。在PLD/FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟。PLD/FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

图1 示出全局时钟的实例。图1 定时波形示出触发器的数据输入D[1..3]应遵守建立时间和保持时间的约束条件。建立和保持时间的数值在PLD数据手册中给出,也可用软件的定时分析器计算出来。如果在应用中不能满足建立和保持时间的要求,则必须用时钟同步输入信号(参看下一章“异步输入”)。

图1 全局时钟

(最好的方法是用全局时钟引脚去钟控PLD内的每一个寄存器,于是数据只要遵守相对时钟的建立时间tsu和保持时间th)

2.门控时钟

在许多应用中,整个设计项目都采用外部的全局时钟是不可能或不实际的。PLD具有乘积项逻辑阵列时钟(即时钟是由逻辑产生的),允许任意函数单独地钟控各个触发器。然而,当你用阵列时钟时,应仔细地分析时钟函数,以避免毛刺。

通常用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,用地址线去控制写脉冲。然而,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:

1.驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

2.逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

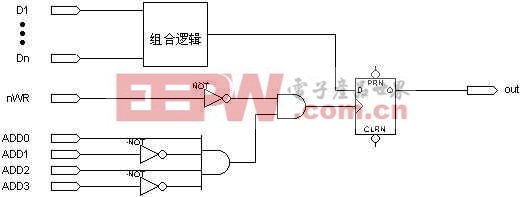

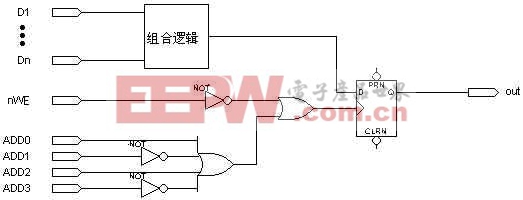

图2和图3 是可靠的门控时钟的实例。在 图2 中,用一个“与”门产生门控时钟,在 图3 中,用一个“或”门产生门控时钟。在这两个实例中,引脚nWR和nWE考虑为时钟引脚,引脚ADD[o..3]是地址引脚,两个触发器的数据是信号D[1..n]经随机逻辑产生的。

图2 “与”门门控时钟

图3 “或”门门控时钟

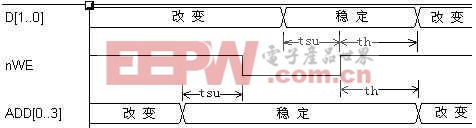

图2和图3 的波形图显示出有关的建立时间和保持时间的要求。这两个设计项目的地址线必须在时钟保持有效的整个期间内保持稳定(nWR和nWE是低电平有效)。如果地址线在规定的时间内未保持稳定,则在时钟上会出现毛刺,造成触发器发生错误的状态变化。另一方面,数据引脚D[1..n]只要求在nWR和nWE的有效边沿处满足标准的建立和保持时间的规定。

无论是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为,并且调试困难、花销很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

1.全局时钟

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。在PLD/FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟。PLD/FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

图1 示出全局时钟的实例。图1 定时波形示出触发器的数据输入D[1..3]应遵守建立时间和保持时间的约束条件。建立和保持时间的数值在PLD数据手册中给出,也可用软件的定时分析器计算出来。如果在应用中不能满足建立和保持时间的要求,则必须用时钟同步输入信号(参看下一章“异步输入”)。

图1 全局时钟

(最好的方法是用全局时钟引脚去钟控PLD内的每一个寄存器,于是数据只要遵守相对时钟的建立时间tsu和保持时间th)

2.门控时钟

在许多应用中,整个设计项目都采用外部的全局时钟是不可能或不实际的。PLD具有乘积项逻辑阵列时钟(即时钟是由逻辑产生的),允许任意函数单独地钟控各个触发器。然而,当你用阵列时钟时,应仔细地分析时钟函数,以避免毛刺。

通常用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,用地址线去控制写脉冲。然而,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:

1.驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

2.逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

图2和图3 是可靠的门控时钟的实例。在 图2 中,用一个“与”门产生门控时钟,在 图3 中,用一个“或”门产生门控时钟。在这两个实例中,引脚nWR和nWE考虑为时钟引脚,引脚ADD[o..3]是地址引脚,两个触发器的数据是信号D[1..n]经随机逻辑产生的。

评论