隔直电容的性能解读

隔直电容通常串接在一个差分链路的每根数据线上,它有很多用途。例如,它可以转换一个信号的平均直流偏置电平,以适合于不同电压标准的逻辑器件。它可以保护发射器、接收器,使之免受因上电序列不良而出现破坏性过载事件的危害。它可以作为电路功能的一部分,检测线路断连的情况。在所有这些应用中,隔直电路都不得损坏通过它的数据。

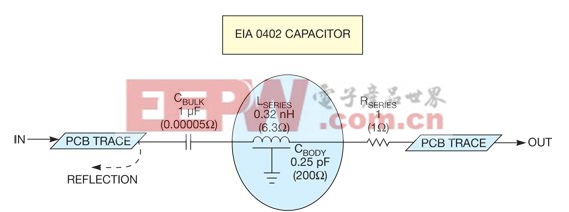

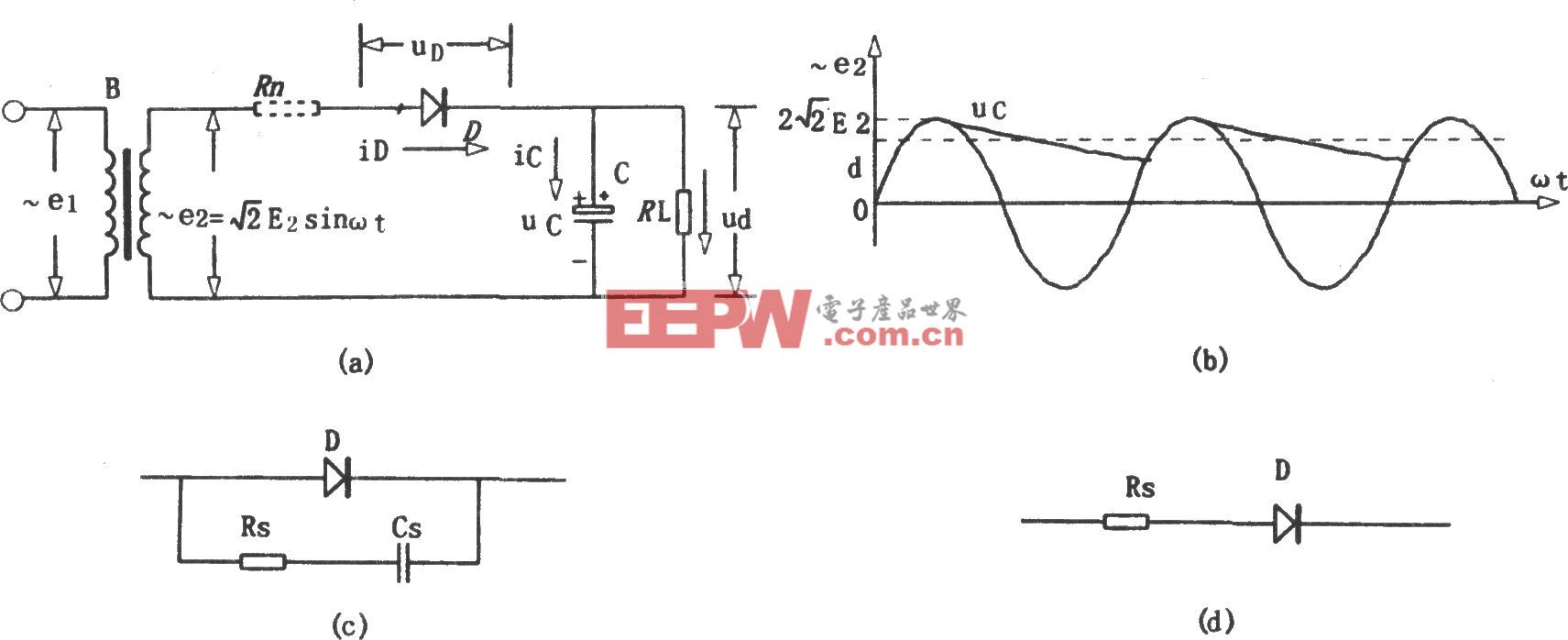

本文引用地址:https://www.eepw.com.cn/article/186361.htm图1给出了一个隔直电容的典型电气模型,可以用一个串行链路将其串接。该模型显示了一个PCB走线的输入和一个输出。实际上,电容是焊在连接输入与输出走线的焊盘上。电气上看,图中用一个逻辑图替代了实际的电容,该逻辑符号包括三个主要元件,都是电容的标准电气模型。CBULK 表示元件的标称电容。LSERIES 是与焊盘、过孔和信号电流所穿过电容体任何部分相关的布局电感。RSERIES 是元件的等效串联电阻。图1列出了一个普通EIA 0402尺寸6.3V电容的典型值。图中亦包含了第四只元件CBODY。该元件表示实际电容体与所有其它邻近物体(包括参考面)之间的寄生电容。

图1 在一个隔直电容中,在3.125 GHz时,CBULK和RSERIES的阻抗是可忽略的。LSERIES和CBODY的值最关键。

在任何电路分析中,第一步都是对电路阻抗做一个快速评估,看是否可以忽略掉任何元件。假设链接速率为6.25 Gbps,交错101010模式(可以做出的最快模式)的频率等于3.125 GHz。图1列出了这一频率下,四个模型元件的阻抗大小。

体电容与串联电阻的阻抗可以忽略不计;串联电感与寄生并联电容是主要的成份。电路看起来像一个针对分布式传输线的梯形模型单稳态部分。电路的阻抗等于

当一个上升沿到达输入终点时,如果电路的体电容过大,而串联电感过小,则阻抗小于PCB走线的阻抗,电路表示为一个简单的负脉冲。另一方面,如果电路的串联电感过大,而体电容过小,则阻抗大于PCB走线的阻抗,电路表示为一个简单的正脉冲。将电感与电容调节到正确的比率,电路就变得几乎完全电气透明。这就是优秀隔直电容性能的秘密。

一种降低体电容的方式是在电容下方的参考面上,切割出一个小的圆形空洞,从而对地释放了电容,并略微增加了串联电感。这两个结果都提高了电路的阻抗。

一名模拟工程师可能建议说,可以主动地缩小体电容的值,直到由体电容和串联电感所形成的串联谐振频率与3.125 GHz相适应。不幸的是,只有在窄带情况下,以这种方式调节体电容才会获得利益,并且仍留有寄生体电容,产生出反射。增大储能电容,直到其阻抗可以忽略,这样就只要考虑串联电感和体电容。这些元件之间可以做均衡,以获得几乎理想的性能。

评论