地弹对电路的影响分析

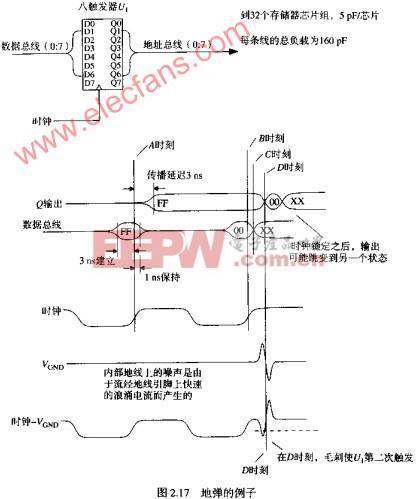

图2.17说明了地弹的情形。设想一个TTL D型八触发器,由单一时钟输入,驱动一组32个存储器的芯片组,以每条输入线5PF计算,每条地址线的负载为160PF。

本文引用地址:https://www.eepw.com.cn/article/186237.htm

假设进入D触发器输入点的数据建立时间较长而保持时间较短,图2.17中出现的数据为3NS建立时间的1NS保持时间。设定这个时序符合我们的TTL八触发器的要求。

在时钟边沿A,这个触发器锁存了数据码字FF。在时钟边沿B,触发器锁存的数据码字为00。在这两种情况下,该触发器3NS的传播延迟都长于所需的保持时间。

在C时刻,使输入数据变化为任意码字XX。C时刻紧接在时钟脉冲B之后1NS。此记得触发器的内部已尼锁存为00码字,但是Q输出端尚未从FF转变到00。

图中倒数第二个波形典线为VGND。在A时刻之后,当Q输出跳变为正、负载充电电流入VCC引脚,而不是地引脚,因此在VGND上没有出现噪声。在D时刻,所有八个输出都跳变到LO,我们看到一个大的VGND噪声脉冲。这个噪声脉冲引起了一个逻辑错误,称为双重触发。

双重触发是由时钟电路中的差分输入运算所导致的,在触发器内部,时钟输入通过比较芯片时钟引脚与地引脚间的电压差而得到。图2.17底部的典线显示了这个电压差。这个差分波形在B点有一个干净的时钟边沿,紧接着是由信号电流流过地引脚而引起的一个大的毛刺。触发器将在这个毛刺脉冲中再触发。

如果数据输入的变化发生在D时刻的第二个时钟处,触发器将会跳转到状态XX,相应的Q输出在D时刻暂时翻转到正确状态,但随后却不可思议地翻转到某个错误状态。

从外部观测时钟输入,显示的是一个完全干净的信号,错误只出现在器件封闭内部。

双重触发错误经常发生在双列直插封装的触发器内,出现在非常快速的输出驱动器连接较重容性负载的情况。双列直插封装的FCT系列的多嘴锁存器也会出现这一问题表面贴装的器件由于引脚较短,因此不容易受到双重触发的影响。因为新一代触发器跳变得更快,我们需要采用新型的、接地电感少之又少的封装形式来进行封装。

倘若为输出驱动器提供专用电源引脚,与那此用于输入信号的参考地引脚隔离,就可以很好地避开地弹的问题。既然没有电流流入输入参考地引脚,也就没有地弹效应发生。大多数ECL系列和许多类型的门阵列,都为此而使用了专用的电源引脚。

边沿触发的输入线,例如复位和中断服务线,也特别容易受到地弹脉冲的影响。

DIY机械键盘相关社区:机械键盘DIY

评论