使用采样保持技术实现运算放大器建立时间测定

引言

现代高速运算放大器 (op amps) 的建立时间都为几纳秒左右。这个时间是如此的短暂。因此,要想在某个合理误差范围内对其进行测定,不仅仅对自动测试设备(ATE)是一个难题,即使在工作台上也难以完成。今天的运算放大器产品说明书中,常常以模拟值的形式给出产品的建立时间数据,原因是在工作台上对其进行测试需要安装更多硬件设备,而这会增加测定的成本和难度。传统的高速示波器仅有一个10比特模数转换器,限制了测量分辨率(最大0.1%)。

本文将介绍一种新方法,其经过证明可以有效地完成这些测量工作。它是一种相对低成本、简单的建立时间测量方法。这种方法把准确性和精确度建立在波形生成器和采样保持电路的相对速度上。

受测器件的步进输入

本文中,建立时间是指使用某个理想步进输入,到受测器件(DUT)进入并维持在某个规定误差范围(终值对称)内的时间。理想步进输入很容易在模拟中产生得到,但在实验室中却没有能够产生理想步进波形的仪器设备。即使在理想条件下,过阻尼和高阻尼仪器的输出可能需要一些RC时间常量,以单调地稳定在0.1%终值范围以内。

对于一些欠阻尼系统而言,步进波形会超出终值,并且可能会出现振铃。实际上,即使是高阻尼系统也会有欠阻尼现象。一般而言,步进波形下降越快,过冲和振铃也就越多。之后,这种非理想状况传播至受测器件的测量输出波形。幸运的是,利用计算机日志记录输入和输出数据,通过排列这两种数据并用输出减去输入便可实现输出标准化(受测器件使用同相单位增益配置)。

平底脉冲生成器

波形生成器降沿用作受测器件的输入时,可以使用一个平底脉冲生成器(FBPG)来平整生成信号的低压电平。平底脉冲生成器将降电压钳制接地,代价是出现更大的过冲。这样便让测试工程师能够通过测试装置调节平衡实现一定程序的控制。同样,我们可以使用平顶脉冲生成器来平整高压电平。

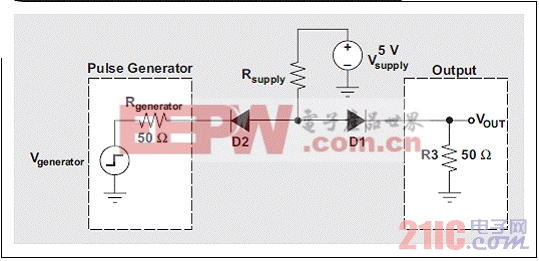

图 1 显示了两个背靠背放置的高速齐纳二极管,每个二极管都有一个单独、可调节电源。一般原则是,按照如下顺序启动装置:调节Rsupply,

获得D1/D2连接5V电压,然后调节Vgenerator输出电压,让其在2V高压和-5V低压之间摆动。这样便可在2Vpp高压电平和0V低压电平下对输出进行偏置。当Vgenerator为高时,D2关闭,D1开启。在此期间,输出电压成为D1正向电压(Vsupply)的函数,同时也是流经Rsupply和D1电流量的函数。当输入为低时,D1关闭,D2开启。在此期间,输出电压摆至接地电压,同时其转换速率与流入相应电阻器R3的电流大小成正比例关系。瞬态响应与二极管电容、反向恢复时间和正向恢复电压有关。

图 1 平底脉冲生成器 (FBPG)

由于二极管的非线性特性,需使用严密的方程式来计算DC电平和平底脉冲生成器瞬态响应。作为一种替代方法,也可以在软件(例如:德州仪器公司的TINA-TI™)中模拟这些方程式。假设脉冲生成器的速度非常快,则输出波形的降时间和过冲与二极管的速度和恢复时间有关,同时也与寄生电容和安装平底脉冲生成器的印刷电路板(PCB)的电感有关。换句话说,设计人员应该选择最快速、最健壮的二极管,并在将平底脉冲生成器用于高速波形生成时遵循优秀PCB布局原则。

建立时间测量的采样保持方法

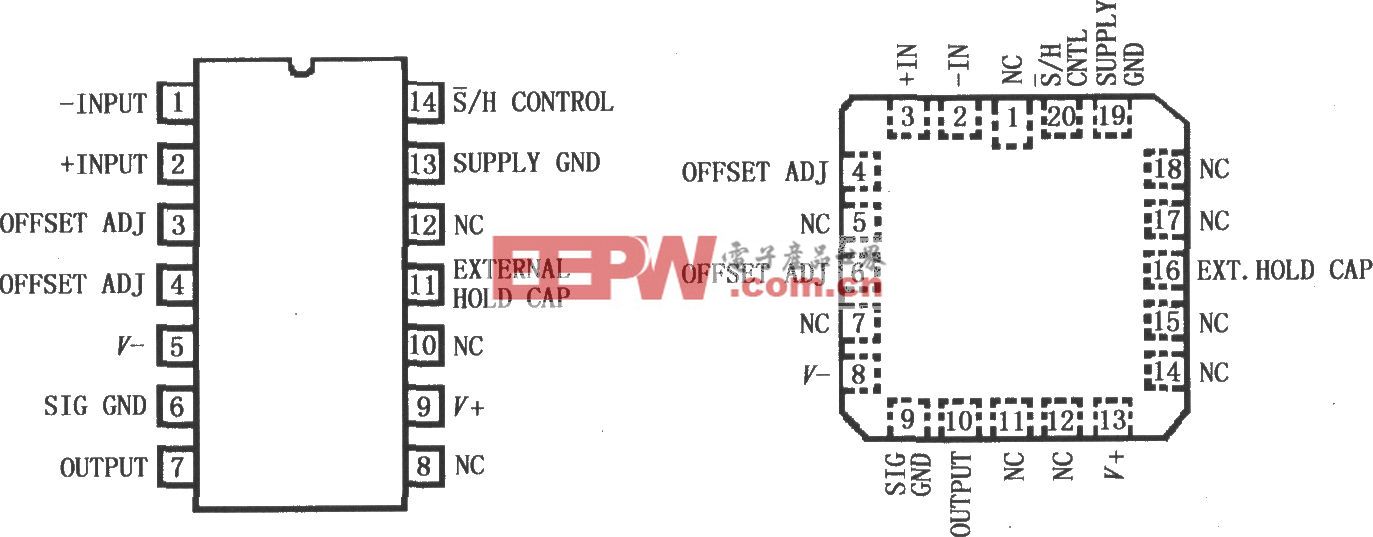

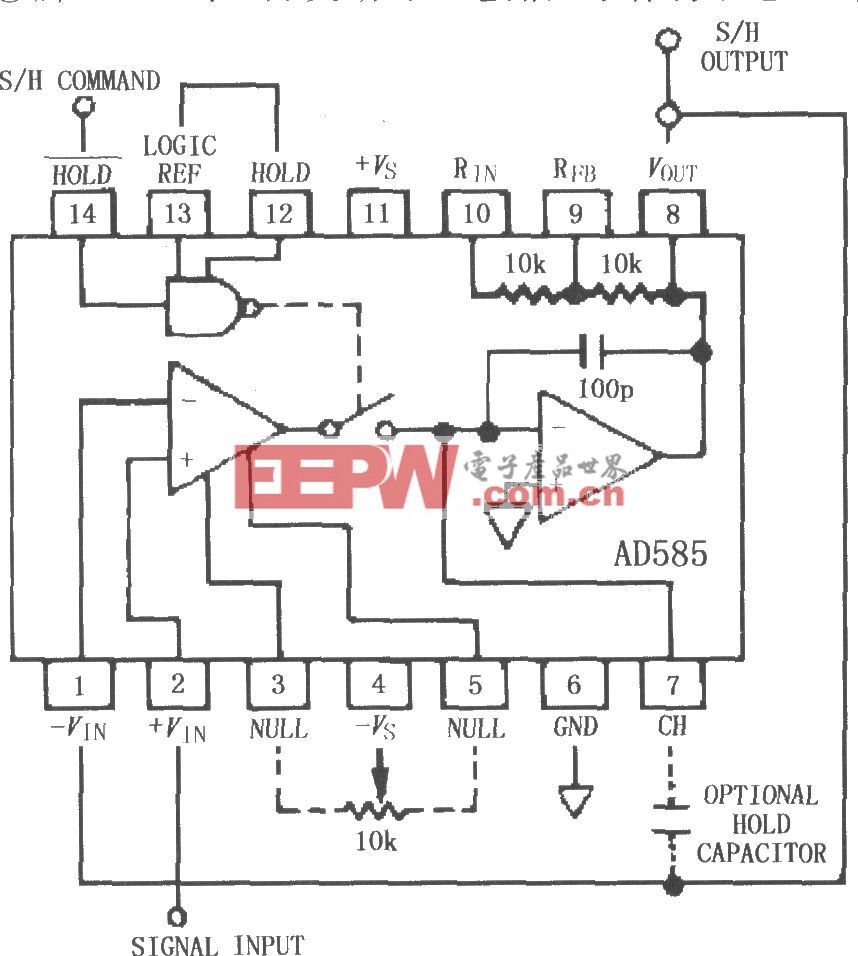

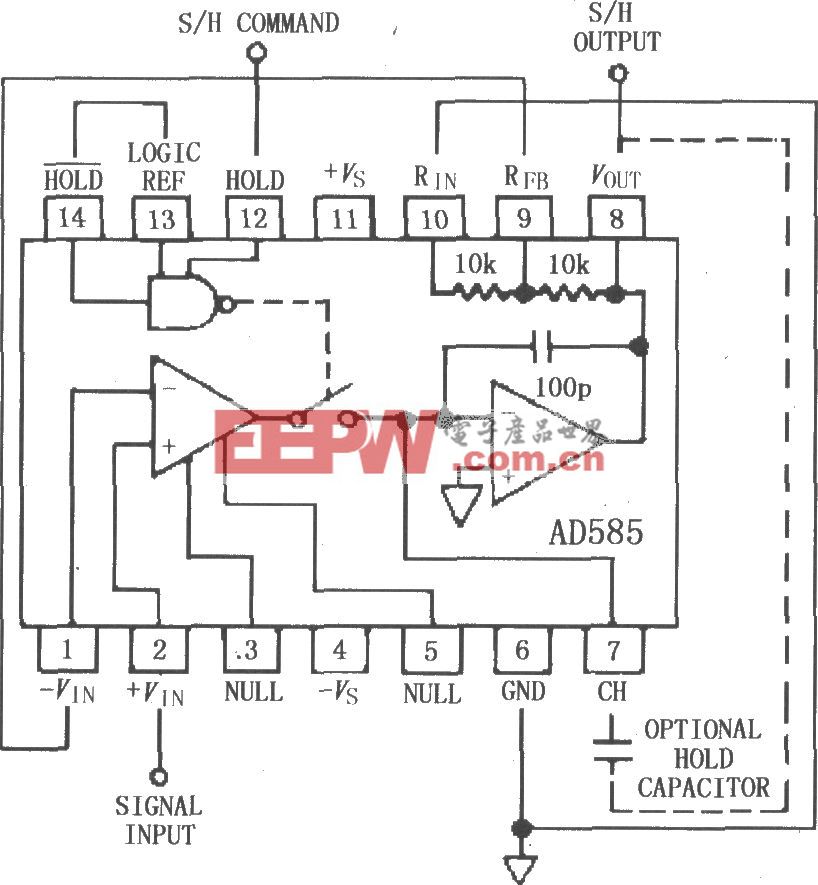

就这里介绍的例子而言,我们选择使用TI的OPA615(见图2)来实现建立时间测量的采样保持(S/H)功能,这是因为:它拥有宽带运算跨导放大器(OTA),针对低输入偏置电流进行了优化;另外,它还拥有快速、精确的采样OTA(SOTA),其同时起到一个比较器和缓冲器的作用。当保持控制引脚为高时,通过SOTA在电容器(CHOLD)上对模拟输入(VIN)采样。当保持控制引脚变低时,CHOLD电压在输出(VOUT)端得到保持和反射。采样期间,CHOLD电压被调节至输入实时电压电平。如果输入和CHOLD之间的差异较大,并且采样时间仅为几纳秒,则要求高转换速率。保持期间,CHOLD电压始终充电/放电,原因是其漏电流和OTA所需的偏置电流。电流反馈环路可确保SOTA转换速率足以捕获VIN的正确电压电平。

评论