抑制PCB对直流电源噪声干扰的滤波器设计

摘要:采用电路测量的方法设计一款通用滤波器,用来抑制数字电路板给直流供电电源带来的噪声干扰。介绍了双探针测量技术,使用双探针法测量出直流供电电源和印制电路板在实际加电工作中的阻抗,用测量出的阻抗信息,选择出合理的滤波器拓扑结构,并通过计算确定元器件值,而并不需要反复做实验和付出额外的代价。通过实际进行的测试,验证了这种滤波器的有效性和可行性。

本文引用地址:https://www.eepw.com.cn/article/185879.htm0 引言

为抑制电磁干扰(EMI),通常在印制电路板(PCB)的输入电源端放置EMI滤波器。在实际应用中,一个电子产品中的几块PCB板常共用一个直流供电电源,这样造成一块PCB上的噪声干扰到另外一块PCB上的电路。使用电源滤波器可以抑制共用一路电源的PCB板间的耦合噪声。

1 方案设计

设计PCB上的电源EMI滤波器时,要么按照芯片资料的推荐电路来设计,要么通过试验来确定滤波器的布局和元器件值。但是对于一块指定的PCB来说,没有通用的方法来设计EMI滤波器,这样就造成了设计时的困难。该文的目标是设计一种通用滤波器,但前提条件是PCB上的噪声、阻抗和电源是已知的或是可求的。在已知噪声和阻抗的情况下可以设计出最优的EMI滤波器。

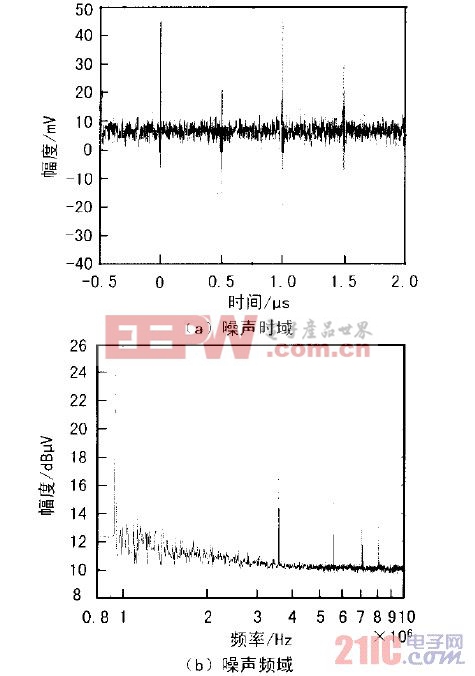

为了测试这种设计,用线性电源(0~32V,5A)来给数字PCB供电。这样选择的线性电源不会引入高频噪声影响测试结果。直流输入噪声的时域和频域图如图1所示。图1中可以看出,频率1MHz的噪声最大,因此EMI滤波器要抑制频率为1MHz的噪声。

图1 直流输入噪声的时域和频域

EMI滤波器通常要削弱5次以上谐波来减少共用电源上其他电路引入的噪声。然而如果测得的基础噪声频率小于10MHz,设计时要滤掉9次谐波。

在该案例中,测的基础噪声主要在1MHz,测量带宽是0~10MHz,包含9次谐波噪声。PCB的供电电源输出阻抗和直流输入阻抗可用双探针电路测量方法测出,这样就可以设计出有效抑制EMI的滤波器。

1.1 双探针测量法

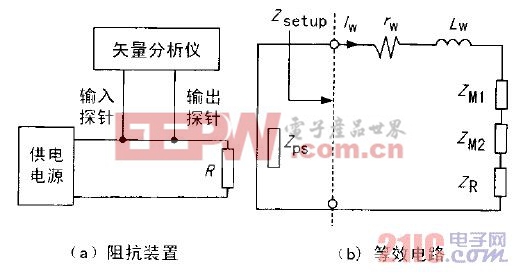

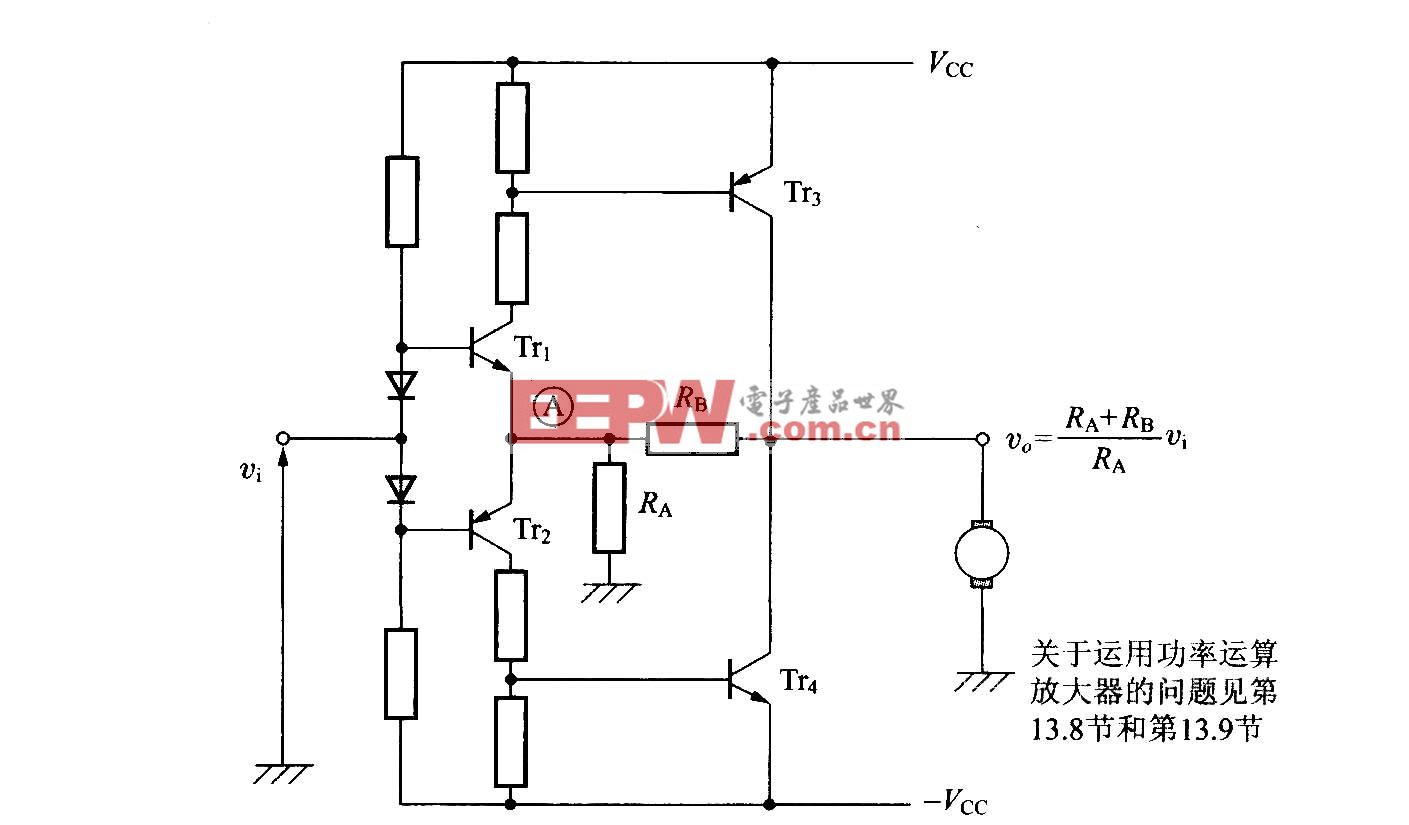

图2简要地描述了双探针测量供电电源输出阻抗的基本理念。测量装置如图2(a)所示,供电电源串联负载电阻R。2个探针分别接至矢量分析仪(VNA)(RS ZVB8)的端口1和端口2上,并接入电路用于输入和接收信号。正常工作时,供电电压6V,输出电流3mA.因此等效电路选取R=2kΩ。

为了减少电流负载引起的干扰,把2个电流探针的等效电路接入电路。通过把双探针接入电路反映出的阻抗特性,等效电路如图2(b)所示。双探针的阻抗分别为ZM1和ZM2,LW和rW为等效电感和电阻,VM1为VNA端口1的等效电压。

图2 双探针测量阻抗装置及等效电路

由图2(b)知,环路电流为:

式中,Zsetup=ZR+ZM2+ZM1+rW+jωLW;ZX=ZPS。

环路中输入信号的电压为:

式中,M1为输入探针与耦合环路的互感应系数;V1为VNA端口1的输出电压;Z1为端口1的输出阻抗;ZP1为从端口1测得的探针阻抗。由接收探针测得的IW为:

这里V2为VNA端口2接收电压,ZT2为由是制造商给出的接收探针阻抗,将式(2)和式(3)代入式(1),可求出供电电源的阻抗为:

式中,

为频率特性参数。

Zsetup和k的值可通过一个用已知电阻代替ZPS等效电路求得。

由此ZPS可由式(4)求出,阻抗变化范围20~120Ω。

把PCB电路板代替ZPS接入图3中,PCB的输入阻抗为:

ZT为实测的PCB连续阻抗,得出ZPCB变化范围200~600Ω。

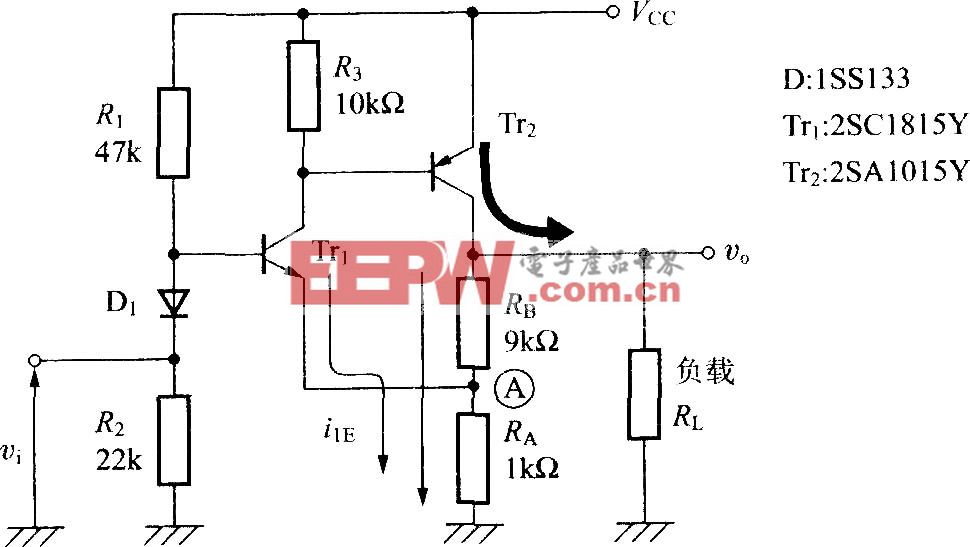

1.2 选择滤波器

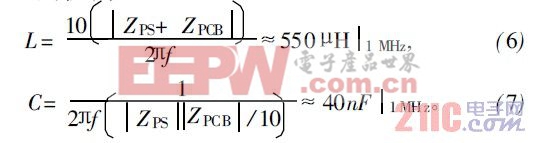

第1步应选定滤波器拓扑结构。常用阻抗匹配的拓扑结构有4种,分别是并联电容、串联电感、L-C回路和C-L回路。ZPS和ZPCB的阻抗都在几十欧至几百欧间,若采用并联电容拓扑结构,并联电容的值要远小于ZPS ||ZPCB的并联电容,若采用串联电感拓扑结构,串联电感的值要远大于ZPS+ZPCB的串联电感,按并联电容和串联电感拓扑结构分别估算出C和L的值为:

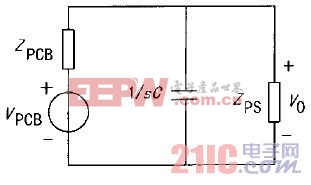

由于电感的计算值为550μH,其体积远大于电容的体积,因此选定并联电容拓扑结构,等效电路如图3所示。

图3 并联电容滤波器的等效电路

带滤波器比不带滤器时衰减值为:

电源滤波器相关文章:电源滤波器原理

评论