AD9230在中频数字接收机中的应用

摘要:中频数字接收机对ADC有很高的要求,ADC的精度和转换速率必须足够高,以实现对中频信号的采样。AD9230是1 2位精度、最高速率达250 MSPS的ADC芯片,可为一般中频处理系统提供足够的动态性能。对AD9230的主要原理功能进行了描述,对关键管脚进行了介绍,最后给出了基于AD9230的数字中频接收机工程应用实例,为基于AD9230的中频数字接收机设计提供了参考依据。

关键词:AD9230;ADC;数字接收机;高速采样

0 引言

中频采样电路中采用正交通道,由于I,Q分量在数字域而不是在模拟域中被分开,从而避免了模拟域中由于I/Q通道不匹配所引起的误差。在数字域中,正交分量的幅度和相位一致性很高,可以获得比模拟处理更高的性能。随着数字信号处理技术的不断发展和芯片处理速度的不断提高,采用数字中频技术的方案越来越成熟。

ADC是模拟和数字信号处理的桥梁,在很大程度上决定了数字中频处理系统的整体性能。AD9230是模拟公司的高速率12位ADc芯片,采用AD9230可给系统提供高质量的采样精度和速率。本文介绍AD9230的主要功能和应用。

1 AD9230功能介绍

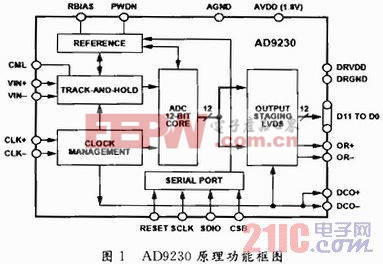

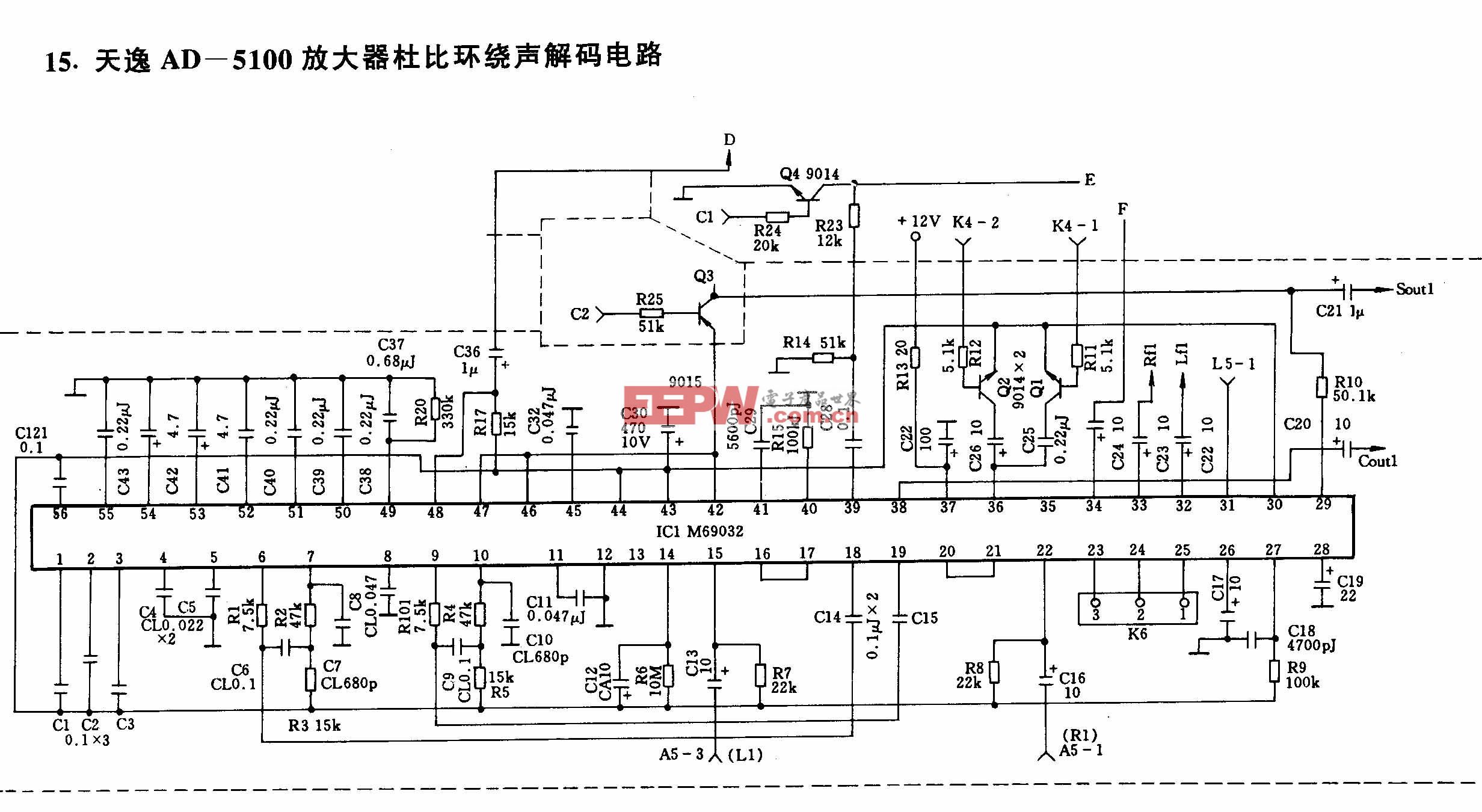

AD9230是高性能低功耗的模拟数字转换器,其采样率最高可达250 MSPS,适合在宽带处理系统中应用。它在片内集成了跟踪保持(T/H)和基准电压,工作时只需1.8 V电源和一个差分驱动时钟。AD9230的数字输出为LVDS(ANSI-644)兼容电平,支持补码或偏移二进制码输出。其工作温度范围为工业级(-40~+85 ℃)。AD9230原理功能框图如图1所示。

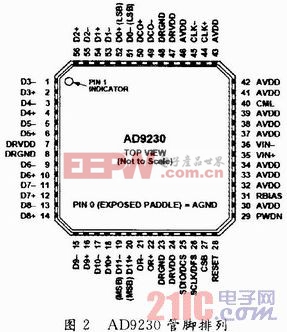

AD9230采用LFCSP封装,其管脚排列如图2所示。

从图2可看出,基于高速应用场合的要求,AD9230的模拟输入VIN、数字时钟输入CLK、数据输出D0~D11、数据同步时钟DCO都采用差分方式。CSB,SCLK,SDIO三条串行接口引脚用于访问AD9230内部工作寄存器,可渎取工作状态或写入控制指令。其余主要管脚功能:AVDD和AGND分别为模拟电源和模拟地;DRVDD和DRGND分别为数字电源和数字地;RESET为复位脚;PWDN为待机控制;CML为共模电压输出。

高速采样对工作时钟要求很高,时钟抖动引起信噪比下降。AD9230需要差分输入时钟以保证性能,单端时钟可通过变压器耦合进行转换。高速ADC一般使用时钟两个沿产生内部定时信号,因此ADC对时钟占空比很敏感,通常允许5%误差。AD9230包含一个占空比稳定器(DCS)可产生50%占空比的内部时钟信号,这样宽范围的时钟占空因数不影响AD9230的性能。

2 AD9230在中频数字接收机中的应用

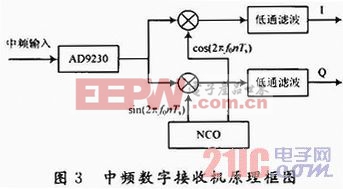

采用中频带通采样的中频数字接收机原理框图如图3所示,中频数字接收机系统的主要技术指标如下:中频频率为140 MHz;信号带宽为8 MHz;调制方式为QPSK。

AD9230的采样频率和NCO的系统工作时钟都取为160 MHz。140 MHz中频信号被160 MHz采样可得到数字域的20 MHz中频信号,NCO输出20 MHz正交本振与其进行数字域的正交混频,数字低通滤波器滤除混频产生的40 MHz倍频项可得到基带的I,Q信号。

3 结论

中频数字接收机采用数字处理避免了模拟处理I,Q通道幅度和相位不一致所引起的误差,也避免了模拟电路的直流偏移效应,具有更好的性能。数字化处理部分可由软件来完成,通过改变程序就可改变功能,更加灵活。鉴于这些优点,中频数字接收机得到了越来越多的重视。

ADC是中频数字接收机中的重要器件,文中介绍了高速AD9230的原理框图和主要管脚功能,给出了一个工程应用实例,为基于AD9230的中频数字接收机设计提供了参考依据。

评论