一种高精度低电源电压带隙基准源的设计

输出不随温度、电源电压变化的基准电压源,在模拟和混合集成电路中应用广泛,特别是在高精度的场合,基准电压源是整个系统设计的前提。

由于带隙基准电压源具有较低的温度系数和高电源电压抑制比,以及能与标准CMOS工艺相兼容等优点,因而成为常用的基准电压源实现方式。文献设计了具有温度补偿的传统带隙基准电路,但其电源电压和温度系数过高,且输出电压约在1.25 V,难以满足低压的要求。文献设计了低电源电压带隙基准电路,但输出基准电压过高。文献提出了解决方法,设计了低压带隙基准源,电路结构复杂。

文在分析几种基准源的基础上,采用0.25 μmCMOS工艺设计了一种低电源电压、低输出电压、高电源电压抑制比、高精度的带隙基准源,经Hspice仿真表明设计的电路具有良好的性能。

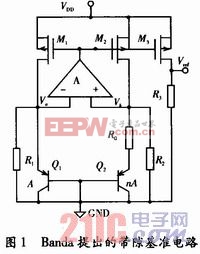

1 Baftda提出的低压带隙基准电路

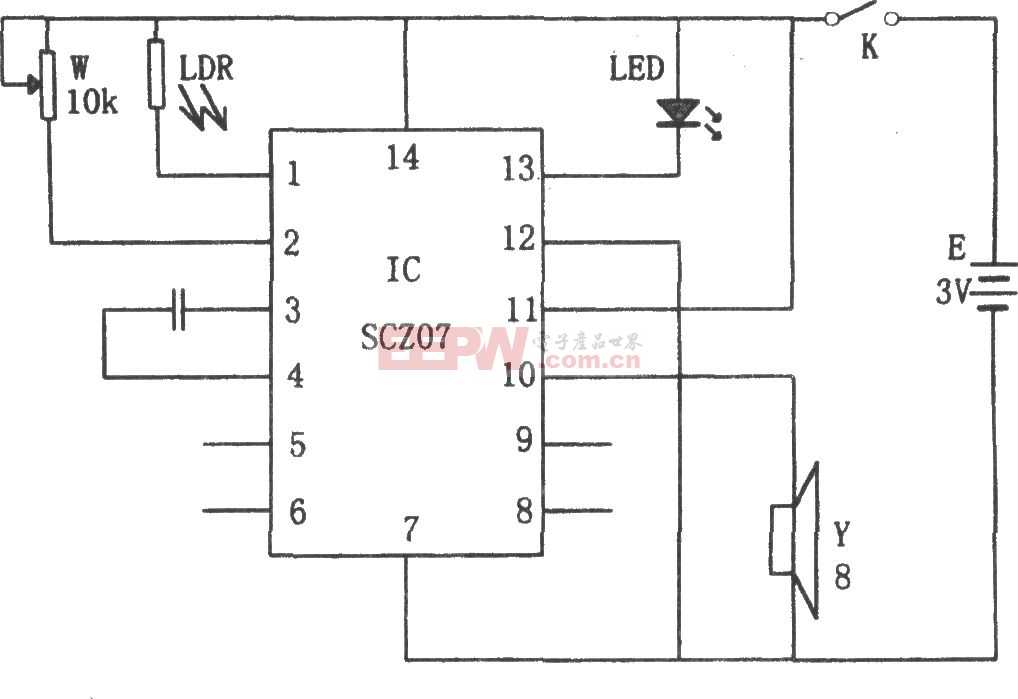

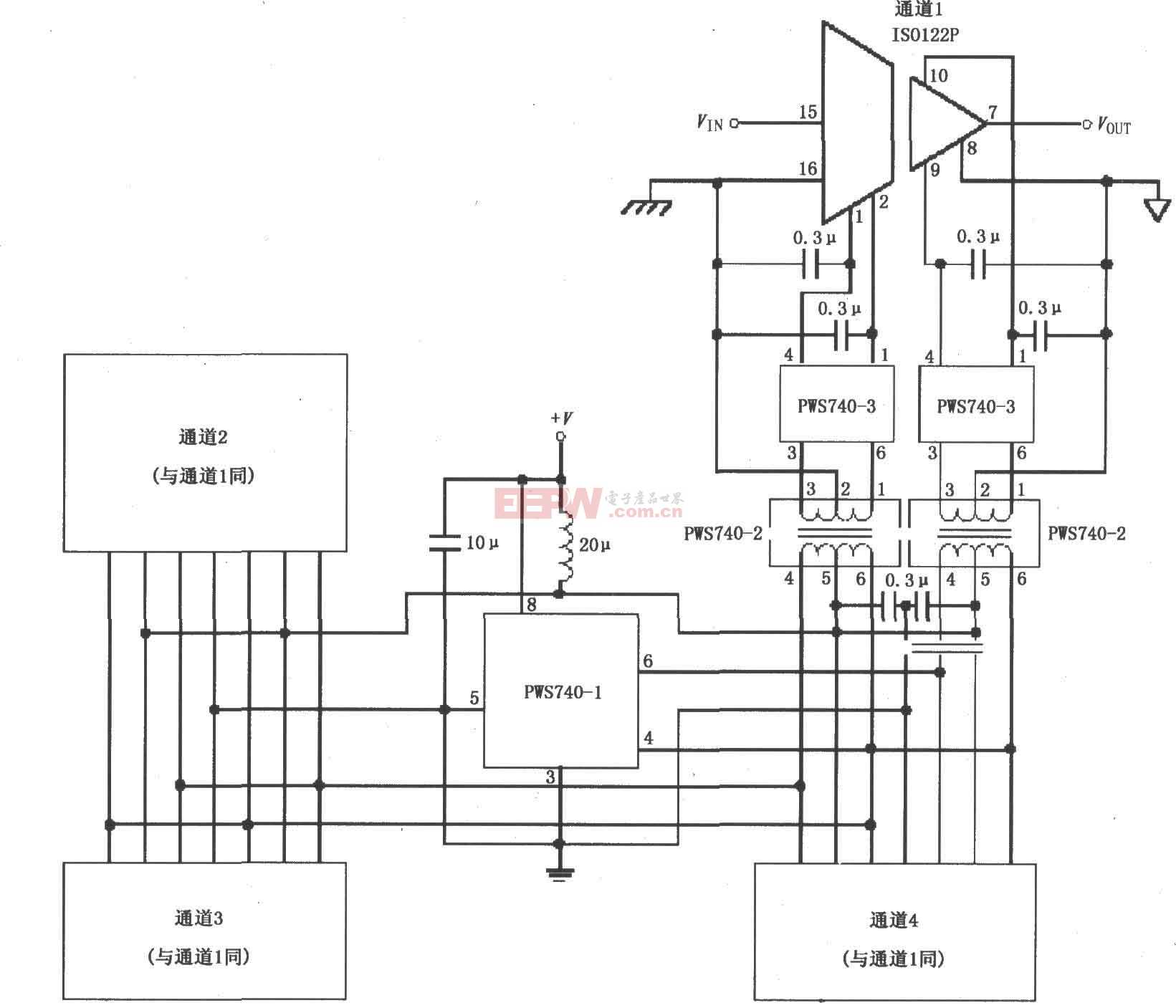

统的带隙基准电路的原理是将两个具有相反温度系数的电压以适当的权重相加,基准电压的典型值约为1.2 V。Banda提出了电流求和型带隙基准电路,对产生的正负温度系数的电流加权求和,然后让这个电流流过电阻,产生和温度无关的基准电压,如图1所示。M1和M2,M3管的尺寸相同,R1和R2的值相等,输出的基准电压近似为

![]()

只要调整R2和R3的比值,就可以控制带隙基准电压的数值,得到低于传统带隙基准电压的值。

带隙基准电路的电源电压的最小值受到两个限制

(1)输出基准电压的大小限制了电源电压

![]()

其中,VSDati为工作在饱和区的CMOS管的源漏极电压

(2)运放的输入电压也会限制电源电压

如果运算放大器采用PMOS差分输入,最小电源电压

![]()

在这两个因素的限制下,带隙基准电路的电源电压一般在2 V以上。本文从两个方面入手,设计了低电源电压、低输出电压、高精度带隙基准电路。

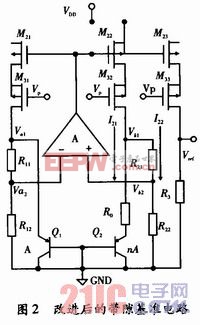

2 电流求和型带隙基准电路

图1所示的电路解决了低基准电压源的产生问题,但对电源电压的要求仍较高。文中作了以下改进:(1)为了减少输出基准电压对电源电压的敏感度,引入了共源共栅结构,其偏置电流由与电源无关的偏置电路提供。(2)文献中没有给出具体的放大器,因此补充设计了运算放大器。(3)为了保证PNP管正常工作,图1中运放输入端Va、Vb点的电压大约在700 mV,这限制了电源电压的进一步降低。本文将电阻R1和R2分别分成两个电阻R11、R12和R21、R22的串联,通过电阻分压使运放的输入端Va2、Vb2的电平在250 mV左右,如图2所示。由运算放大器和MOS管组成的反馈系统可迫使Va2=Vb2,设计电阻R11=R21,R12=R22,可以保证Va1和Vb1也相等。

M21,M22和M23管的尺寸相等,使3个支路的电流大小相等。

其中,R2=R21+R22。

通过电流镜将I21和I22之和镜像到输出端,可以推导出带隙基准电压

![]()

可见,可以通过调节电阻R0、R2的大小使输出电压的温度系数为0,调节电阻R3、R2的大小可得到低于1.2 V的带隙基准电压。

评论