基于Atlas的MFIS结构器件电学性能模拟

3.3 绝缘层材料对MFIS结构器件的影响

由式(1)可以看出,具有高介电常数εi的绝缘层,能够使分配在铁电层上的有效电场增加,从而使铁电层趋于饱和,产生一个较大的记忆窗口。为研究不同绝缘层材料对MFIS器件相关性能的影响,利用Arias软件对采用SiO2、Si3N4、Y2O3、HfO2及CeO2作为绝缘层的MFIS器件的C—V特性及记忆窗口进行了模拟和分析。

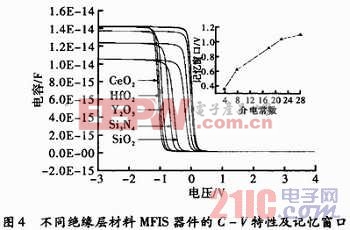

图4给出了在5 V的应用电压下,分别采用不同绝缘层材料时MFIS器件的C—V特性及记忆窗口。从图中可以看出,MFIS器件的C—V曲线随绝缘层介电常数的增加逐渐变宽,其记忆窗口从0.36 V增大到1.09 V,并逐渐趋于饱和。

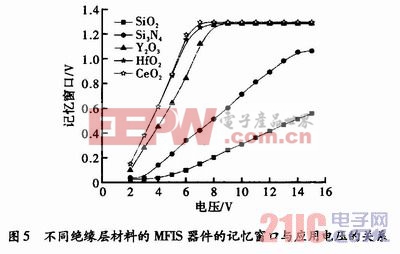

图5为不同绝缘层材料时MFIS器件的记忆窗口随应用电压的变化。从图中可以看出,高介电常数为绝缘层jf,MFIS器件的记忆窗口在7 V时达到饱和,而低介电常数为绝缘层时,记忆窗口在15 V时仍未达到饱和。这意味着在一定厚度下,高介电常数的绝缘层能够使MFIS器件的记忆窗口在一个较低的应用电压下达到饱和,从而减小工作电压,使得其与现代集成电路设计工艺相兼容。

4 结束语

利用器件模拟软件Arias,结合饱和状态及非饱和状态下的铁电极化模型,研究了应用电压、绝缘层厚度及材料对MFIS器件的C—V特性及记忆窗口的影响。仿真结果表明,增加应用电压、减小绝缘层厚度及采用高介电常数材料,可以使器件的C—V曲线逐渐变宽,记忆窗口逐渐增大。但是考虑到MFIS器件与现代集成电路的工作电压的兼容性,以及过薄的绝缘层可能会引起的漏电流,使得采用高介电常数的绝缘材料作为MFIS器件的绝缘层成为一个提高MFIS器件性能的有效途径。

评论