最新全能数控电源IC-ADP1043A(六)

摘要:随着数字技术的发展和成熟,电源产品更多地向数字化方向发展。采用数字技术可减小电源高频谐波干扰和非线性失真,同时便于CPU数字化控制。文中重点介绍了ADP1043A的功能、原理及具体应用细节。ADP1043A的创新架构能支持多种拓扑结构,其图形化的操作界面、丰富的监控和管理功能,非常方便技术人员操作,也改变了以往对数字电源的认识。

关键词:ADP1043A;EEPROM;OrFET控制;同步整流(上接第9期)

5 通讯系统

5.1 I2C接口

ADP1043A的控制通过I2C接口被载出,ADP1043A接到I2C总线作为从属元件,由主控器件控制。

5.2 I2C地址

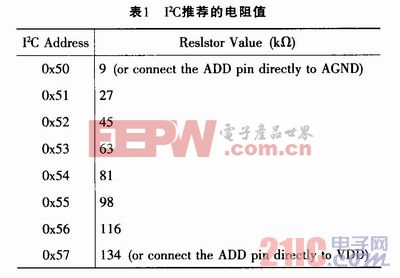

ADP1043A的I2C地址有外部从VDD端接到AGND的外部电阻来设置,表1列出了推荐的电阻值及相应的地址,8个不同的地址可用。

如果一个不正确的电阻值被用上,结果I2C地址会紧靠两地之间的临界处,一个标志就被设置出来。

在表1中推荐的值可以变化±2kΩ,ADP1043A扔回相同的地址。因此,推荐选择1%精度的电阻用于ADD端。

I2C地址0*58是广播地址,它允许多个部分同时写入,用广播地址提到表1中的I2C专用地址,所有ADP1043A器件的I2C总线都会写入,广播地址仅能用于写命令。

5.3 通用I2C时段

ADP1043A有一时段送出特色,以保护SDA线上的对应的故障条件,I2C接口监视SDA线。如果它停在低电平时间为0.65mst_low1.3ms,则I2C接口即复位,等待另一次起始条件。

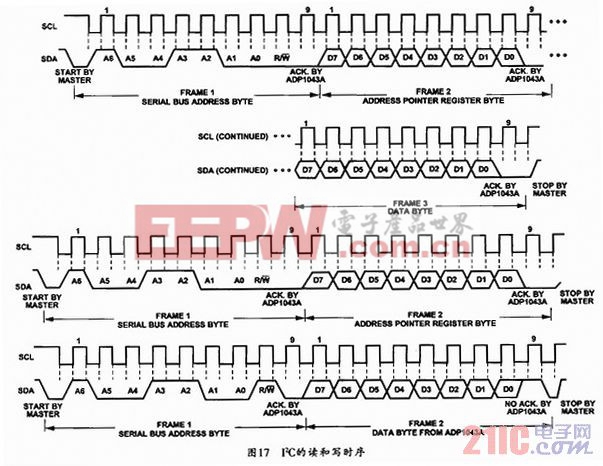

I2C规范定义出专门的条件,给不同类型的读和写的操作,一般I2C的读和写的操作展示在时序图中,如图17所示,并在此部分描述。

(1)主控初始数据传输用建立一个其实条件,定义了高电平到低电平传输为串联数据链SDA,此时串联时钟链SCL仍旧为高电平。这只是数据流在流动,所有从属外部连接到串联总线。响应启动条件并植入下面8位。由一个7位从属地址组成,加上一个![]() 位,它决定出书记传输的方向,即什么数据从从属器件中写入或读出。

位,它决定出书记传输的方向,即什么数据从从属器件中写入或读出。

(2)其并行的地址相应传输地址由加入数据键来响应,在低周期第九个时钟脉冲以前作为已知位,并保持其在时钟脉冲高周期为低,所有其他总线上的期间仍旧是空闲的。此时选择器件要等到数据从写到读出。如果![]() 位是0,则主控写到从属器件中。如果位

位是0,则主控写到从属器件中。如果位![]() 是1,则主控从从属器件中读出。

是1,则主控从从属器件中读出。

(3)数据传送整个串联总线为9个时钟脉冲的顺序,数据的八位跟随由从从属期间定下的位。数据链的传输在时钟信号低周期时必须出现。再高的周期仍旧稳定,因为低到高传输是在时钟为高并可以以停止此信号来解释。

(4)如果操作时写入,则在从属地址之后第一个数据位睡觉哦一个命令位,它告诉从属器件什么是期待的下一个,它可能是一个结构,诸如作为告知从属器件所期待的时钟写入,或它可以是一个寄存器地址,它告诉从属器件随后的数据写入在哪里。

(5)因为数据仅能一个方向流动,作为由![]() 位定义的在读出期间它不可能发送一个命令到从属器件。在读出期间以前,它必须首先执行一个写的操作,告知从属器件,读得时间多从短暂。从数据写入到起到与/或地址。

位定义的在读出期间它不可能发送一个命令到从属器件。在读出期间以前,它必须首先执行一个写的操作,告知从属器件,读得时间多从短暂。从数据写入到起到与/或地址。

(6)当所有数据为已经读出或写入时,停止条件建立起来,在写入模式主控器件将数据链。在第10个时钟脉冲到维持停止条件期间拉高。在读出模式,第九个时钟脉冲之前主控器件释放SDA线。但从属器件没有拉低,这是作为没有未承认位已知的。主控器件将数据链拉低,在第十个时钟脉冲前的低电平周期期间,将数据链拉低。然后在第十个时钟脉冲到维护停止条件期间在拉高。

如果几个读或写的操作必须逐渐地执行,则主控器件可以送出一个重新开始的条件,以代替停止条件,去开始新的操作。

评论