基于SOPC的通用字符VGA显示电路设计

摘要:文章介绍了基于Nios II的SOPC的通用字符显示电路的设计,通过实时读取点阵字库信息并输出到VGA端口的方法实现。与传统方法相比,具有简单易行、便于二次开发的特点。以本方法进行了电子万年历的设计,并在基于EP2C35F672C6的DE2开发板上下载验证,结果表明本方法切实可行,适合于实时信息显示。

关键词:SOPC;视频图形阵列字符显示;Nios II

0 引言

VGA(视频图形阵列)是IBM于1987年提出的图形显示标准,虽然早己不是先进的显示标准,但由于其技术和工艺成熟、成本低廉等优势,目前仍有着广泛的应用。

现有基于FPGA的VGA显示系统需要显示字符,尤其是汉字时,通常方法是首先获取所用字符的字模,加入到HDL或C代码中调用。这种方法过程繁琐,且系统通用性不强。本设计以任意字符显示为特点,通过实时读取点阵字库实现字符显示,对存储空间利用率高,且灵活性好,便于进行二次开发。

1 系统硬件设计

本设计使用的是基于EP2C35F672C6的DE2开发板。在SOPC Builder中,将系统命名为system_0,目标板设定为预定义过的“DE2 Board”,加入NIOSII/s软核处理器,在时钟列表中添加50MHz的外部时钟,在组件列表中添加所需组件,如图1所示。

由于本设计的Nios II程序及所使用的字库需要存储在Flash中,因此添加了CFI Flash控制器以及三态Avalon总线,EPCS控制器用于存放FPGA配置信息。LED及JTAG UART组件用于调试中状态反馈,按钮和开关组件用于人机交互,SDRAM组件是本系统的运行内存,最后是VGA显示IP核。

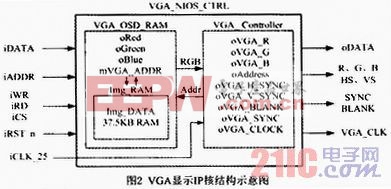

本设计中所用VGA显示IP核符合Avalon总线规范,实现的功能为单色显示,即前景色和背景色各为预先指定的一种颜色,系统启动时核内显存读入一幅单色图像作为初始显示画面。编程时分别以VGA_Set_Pixel或VGA_Clr_Pixel指令将某一像素置为前景色或背景色。此IP核的结构原理如图2所示。

评论