切换式电源的静电放电能力防制技术

先确认因ESD而产生之故障现象,一般来说,ESD造成的故障现象包括:

1. 机台有跳火的现象(不在规划的放电PAD上)

2. 机台进入保护模式(auto or latch)

3. 整个机台损坏。

A. 若机台有跳火的现象,一般为绝缘不足或距离不够所致,对策方式为:

a.1可先用Hi-pot做一二次侧的绝缘测试,将Hi-pot的电压慢慢的往上调整,当一二次侧的绝缘或距离不足时,即为产生跳火而致使漏电流超过10mA,Hi-pot机跳离。尤其是变压器内部或散热片与周边零件的距离,用此法可快速检测机台一二次侧之间的距离问题。

a.2将输入端的火线/中线/地线全部接在一起下地,然后再去测ESD(机台没开机),此方式是检测当有外部电荷进入时,是否电荷是依循规划路径在走,只在放电PAD上有跳火。用此方式可以在不伤机台的情况下(因没有开机)先确认组件之间的距离是否足够,若不够即会跳火。

a.3在ESD测试时,可关灯确认跳火现象是在哪一个部份,一般跳火可用方式为:

a.3.1增加热缩套管,加强绝缘。

a.3.2修改layout,增加组件之间距离。

a.3.3在跳火处涂上白胶,增加其绝缘强度。

B. 若机台进入保护模式,对策方式为

b.1先判断与此现象相关的电路部分,看哪一部份电路动作会导致此保护现象,然后先将此保护模式关掉。例如测试ESD造成电源latch,就先将IC 会进到latch 的功能先Disable,看是否为IC周边线路误动作导致IC进到latch。

b.2若不是保护线路问题,即可能为IC被干扰,对IC来说,操作电流或操作电压愈小的pin脚愈容易被干扰(pin脚呈现高阻抗),确认IC哪个脚位的操作电流很小,设法增加一小电容去滤波或在pin脚前端串联一电阻做干扰讯号的衰减,在切换式电源IC里,CS pin因操作电压较低,故较容易受干扰,因此CS pin的layout 要极为注意;另外,TL431的地也很重要,在规划TL431的地时,最好连接于疏导电路的后端(让大多的电荷先走过疏导电路再进入TL431的地),或于输出端并联一颗MLCC电容再接至此(让此电容做突波的衰减)。

b.3 IC 的所有脚位不可空接, 空接的脚位很容易受外来干扰而被误动作,需以电容或电阻连接至Vcc或接地来拉高或降低其电位。

b.4 IC的Vcc脚也可能因太大的突波而干扰IC内部运作,可串接电阻,并电容来减少突波。

b.5若仍无法找到保护问题,则需用隔离探棒同时量测gate与IC各pin之间的波形,确认是何pin误触IC进到保护模式。

C. 若机台整台损坏,对策为:

c.1机台会损坏表示电荷疏导不足,让电荷进入组件或IC造成损坏,先确认机台的疏导路径是否如之前所提,半导体组件不要经过疏导路径,而疏导路径的铜箔要尽量加粗来使电荷快速放电。

c.2可增加Y电容的容值,降低高频时Y电容的阻抗,增加流过此路径的电荷。

c.3 若IC有高压pin,可在此脚并联一电容来吸收突波电压。

c.4 有些IC的输入/输出端很容易被打穿,在设计上要极小心;输入即为Vcc端,前面有介绍可外加电容,电感或电阻来压制,要注意IC的Vcc绝不能超过其最大额定值,因IC的输出端有一个totem pole,而输出端与Vcc存

在一个上臂的MFET,若Vcc超过此MFET的Vds即可能打穿IC的Vcc至Vgate,让输出一直为高电位。输出即为驱动端,有时会因MFET较大的Cgd而让电荷经由驱动端灌入,可于驱动端串联一电感来抑制其突波电流,或增加一电容对地来吸收突波。

c.5注意组件的选择与layout,对ESD的高频线路来说,寄生电感的影响非常大,在layout 时要将power trace(大电流在走动的线路)布的愈粗,愈短愈好,以减少其寄生电感;而在组件的选择上,侦测电阻也尽量要选用无感电阻。回路上的电感愈大,其感应的逆向电压也愈大,此产生的逆向电压有可能导致IC损坏。

c.6若仍找不出损坏的原因,可用一外加TVS(速度较快),并接于可能发生过电压的地方做限压,或并联一二极管作负压的放电。

结语:

ESD的防制其实重点在于放电路径的规划与相关原理的了解,只要在一开始做电路设计时有先考虑ESD快速放电路径,问题就可以解决一半。而相关原理则包括了解静电测试时的标准测试线路(一个150pF的电容与330?的串联电阻),

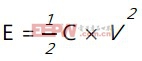

电荷公式Q=C×V与能量公式 ,

,

当电容充满电压并对待测物放电时,待测物上有哪些路径会让电荷走过?哪些组件可以帮助电荷放电,哪些组件会妨碍电荷放电,易受干扰的组件要如何接到讯号源而不受ESD干扰等,利用串联电阻抑制突波电流与电压,串联电感抑制突波电流,并联电容抑制突波电压等方式,可改善大部份ESD造成的干扰问题。

评论