基于二叉树的CVSL电路优化方法

摘要:CVSL,电路不同于互补CMOS逻辑那样具有固定的构成规则,对于复杂逻辑,若不对电路进行优化,则电路速度、版图面积、功耗等性能指标均会受到影响。因此用一种方法有规律的来完成CVSL,电路结构的设计显得十分重要,传统的卡诺图化简法步骤过多,结构不够直观,钟对这一缺陷,提出了用二叉树代替传统的卡诺图法的设计思路,从而使CVSL电路结构得到优化。分析结果表明,二叉树优化法较卡诺图法可使电路获得了更加高效的设计结果。

关键词:电路结构优化;二又树优化法;CVSL电路;互补CMOS逻辑

0 引言

CVSL电路适合于整个系统或模块的高速设计中。在单端式逻辑(Single-ended logic)和差动式逻辑间需要提供互补信号的反相器。对于复杂逻辑,由于两个NMOS Tree有共同项,电路可进一步化简,减少MOS管数量。传统的方法是用卡诺图法,但卡诺图并不能显示出电路的连接关系,若改用二叉树算法,则可以很明了的反映出电路的连接关系。

1 CVSL电路的特点

互补静态CMOS特点电路的特点是P管阵列的逻辑结构正好是N管阵列的对偶,若一阵列是串联,则另一阵列必定是并联。NMOS阵列是原量控制,PMOS阵列是非量控制,因而,N型阵列和P型阵列可以接同一个输入信号。电路中PMOS管的数目与NMOS管的数目相同。如果输入变量共有k个,则总共需要2k个晶体管,形成一种全互补电路。但管子数量多,版图可能比较复杂。只有设计得当,版图才会有规则。

虽然CMOS电路有许多优点,但一般认为其与伪NMOS相比有两大缺点:

(1)CMOS电路的速度比伪NMOS低。任何一级CMOS倒相器至少有两只管子,一只P管和一只N管,它们的栅极是连接在一起的,输入电容加倍,前级的充放电就比较慢。

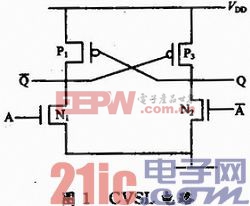

(2)CMOS电路所需的器件数多。一个逻辑电路需要设计两套逻辑函数,分别传送原函数和其补函数。因而,CMOS电路的逻辑冗余度较高。不仅浪费硅片面积,而且增加互联任务,使性能降低。伪NMOS电路只采用一个P管作为上拉负载,以代替全互补标准CMOS电路中的P阵列逻辑。但增加了静态功耗,提高了输出低电平,降低了噪声容限。为克服功耗提出电路的改进方案即CVSL电路,如图1所示。

由于电路同时接收差动式的输入(Differential Input)且提供差动式的输出(Differential Outputs),所以又称为DCVSL(Differential Cascade Voltage SwitchLogic)电路。并且原量反量同时输出。虽然比CMOS所用MOS管数量多,但提供互补输出且由于电子迁移率高于空穴,相同面积下速度比CMOS高(是一种高速设计)。由于存在正反馈,完全消除了Pseudo-NMOS中的静态电流,使输出达到rail to rail(低功耗高噪声容限),进一步提高了翻转速度。

该电路适合于整个系统或模块都用DCVSL,的设计,在单端式逻辑(Single-ended Logic)和差动式逻辑间需要提供互补信号的反相器。对于复杂逻辑,由于两个NMOS Tree有共同项,所以电路可进一步化筒,减少了MOS管数量。

评论