基于DS90UR905Q/906Q设计的24位FPD串并-并串转换方案

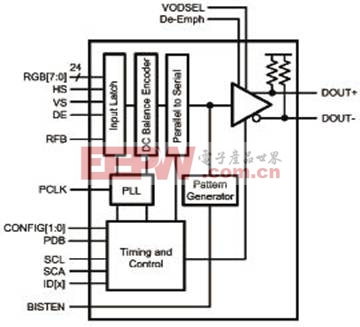

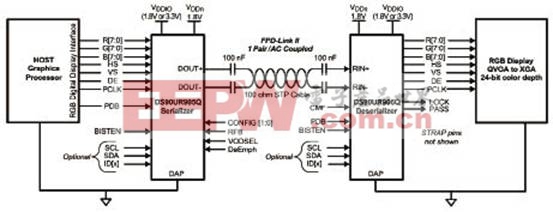

DS90UR905QSer(串行化器)嵌入了时钟、平衡了数据有效载荷,并将信号水平移动为高速低电压差分信号。最多可将24个输入信号同3个视频控制信号串联。它支持24位全彩色或者18位彩色和6个通用信号(如音频I2S)应用。

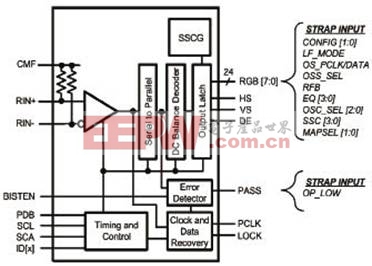

DS90UR906QDes(并行化器)恢复数据(RGB)和控制信号,并从串行数据流中提取时钟。它能够在不使用训练序列或者专用SYNC模式的情况下锁定输入数据流,并且不需要参考时钟。提供链路状态(LOCK)输出信号。

利用用户自定义的去重、差分输出水平选择功能和接收器均衡对串行传输进行优化。利用低压差分信号、接收器驱动强度控制和扩频时钟兼容性将EMI减至最低。可对DES进行配置,从而在其并行输出中生成扩频时钟和数据。

DS90UR905Q(Ser)采用48引脚LLP封装,DS90UR906Q(Des)采用60引脚LLP封装。它们符合汽车级AEC-Q1002级标准要求,工作温度为-40℃到+105℃。

图1DS90UR905Q方框图

图2DS90UR906Q方框图

DS90UR905Q/906Q主要特性

5MHz到65MHzPCLK支持(140Mbps~1.82Gbps)

交流耦合STP互联线缆长达10m

在Ser和Des上集成的终端器

高速连接BIST模式和报告引脚

可选择的I2C兼容串行控制总线

支持RGB888+VS、HS、DE

掉电模式将功率消耗降至最低

1.8V或3.3V兼容LVCMOSI/O接口

汽车级产品:AEC-Q1002级

>8kVHBM且为ISO10605ESD级

后向兼容模式,可以和前代产品协同工作

串行化器――DS90UR905Q

RGB888+VS/HS/DE同1对FPD-LinkII串联

随机函数发生器/扰频器――直流平衡数据流

自定义输出VOD和可调节去重

并行化器――DS90UR906Q

快速随机数据锁定,无需参考时钟

可调节输入接收器均衡

LOCK(实时连接状态)报告引脚

在输出并行总线(SSCG)上的EMI最小化

输出降低驱动强度(RDS)

图3DS90UR905Q/906Q应用框图

DS90UR905Q/906Q应用

汽车导航用显示器

汽车娱乐用显示器

评论