MM58167B 总线型微处理系统实时时钟源

1. 概述

MM58167B作为总线型微处理系统中的实时时钟源,其内部包括一个可寻址的实时计数器、56 bit片内RAM和两个输出中断,而且POWER DOWN引脚的有效信号可使芯片进入省电工作模式。该芯片的时间基准是一个32.768kHz的晶振。其特点如下:

●与微处理器兼容(8 bit数据总线);

●具有从毫秒到月的计数器;

●56 bit内部RAM可与实时时间比较;

●2个中断输出可产生8种中断信号;

●POWER DOWN输入可使所有输入输出失效而只留一个STANDBY中断;

●状态位可指示在一个读周期中是否出现计数更新;

●4年日历(无闰年);

●24小时时钟;

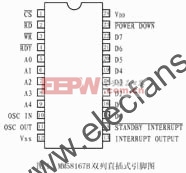

●采用24脚DIP封装(如图1所示)。

2. 功能模块介绍

2.1 实时时钟计数

实时时钟的每个计数器分成十位和个位两个数字,每个数字由4 bit组成BCD码(见表1),任何不用的bit在读时保持逻辑“0”,在写时被忽略。任何不用的bit不参与BCD码的合成。比如小时计数器的十位不应超过2,故只需2 bit表示,而其余2 bit空闲,用短划线(-)表示。

计数器的可寻址部分是从毫秒到月。计数器本身是一个脉动计数器,工作于4.5V以上时的脉动延时小于60μs(工作于2.2V时小于300μs)。

2.2 片内RAM

片内的56 bitRAM可作为一般的数据存储器使用,也可以锁存与实时时钟比较的比较值。每当实时时钟的当前值与RAM中锁存的设置值比较相等时就可以产生报警中断。其中只有毫秒的个位和星期的十位不参加比较(计数器中也未用到,如表1所列)。如果RAM中某个BCD码的最高2个有效位被置为“1”,则认为该位总相等而不参与比较,即被屏蔽掉。因此设置报警中断的规律为:凡是比指定时间单位高的位,设置成0CH(即1100B,最高2位为“1”),而比指定时间单位低的位设为“00H”。比如,希望每天的上午10∶15产生报警中断,则比小时高的时间单位(星期、日期、月)都设为0CH,而比分钟低的时间单位(秒、百分秒、毫秒)都设成00H。

2.3 中断和比较器

该芯片共有2个中断输出。第一个是引脚INTERRUPT OUTPUT(中断有效时输出高电平),该引脚经编程可输出8种类型的中断信号,即10Hz、1Hz、每分钟一次、每小时一次、每天一次、每星期一次、每月一次或片内RAM设置的时间与时钟计数器时间比较相等时产生中断。为了允许某种类型的中断,只需往中断控制寄存器的相应位写“1”,当一个或更多位被置“1”,该位对应的计数器溢出翻零时,将置位中断状态寄存器的相应位并产生中断(使中断输出脚出现高电平),只要读取中断状态寄存器就可以识别中断类型并复位中断,如图2所示。

第二个中断输出是引脚STANDBY INTERRUPT(漏极开路,低电平有效),只要片内RAM中设置的时间与计数器比较吻合,并此中断已经允许(往地址16H的D0位写“1”允许,写“0”禁止),即可产生该中断。

评论