简易数字直流电压表电路及程序

设计一个简易数字直流电压表。(量程0V-2V、测量速度为大于等于2次/秒、测量误差在±0.05V以内,有超限报警、数码管显示。)

3.5.1模块1:系统设计

(1)分析任务要求,写出系统整体设计思路

从试题的要求分析,主要包括的内容为ADC转换电路的控制、采用定时器定时读取ADC转换器的数据、将ADC转换器的数据计算为对应的电压值,最后在数码管上显示出来。

整体设计思路:硬件采用单片机的P0输出数码管的7段码,P2口输出数码管的位控信号。用P1的三个I/O管脚连接ADC转换器的接口,通过查询定时器T0中断标志是否有效来启动ADC转换器的工作,并读取ADC转换器的转换结果。然后,根据ADC转换器的参考电压将ADC转换器的转换结果计算为对应的电压值,并在数码管上显示出来。

(2)选择单片机型号和所需外围器件型号,设计单片机硬件电路原理图

采用MCS51系列单片机At89S51作为主控制器,外围电路器件包括数码管驱动、AD转换器TLC549、基准电压TL431等。

数码管驱动采用2个四联共阴极数码管显示,由于单片机驱动能力有限,采用74HC244作为数码管的驱动。在74HC244的7段码输出线上串联100欧姆电阻起限流作用。

AD转换器的参考电压由精密基准电源TL431提供,标准参考电压Vref+为2.5伏, Vref-为0伏。由于0V-2V内的测量误差控制在±0.05V内,因此8 位A/D转换器即可满足要求。AD转换器TLC549是以8位开关电容逐次逼近A/D转换器为基础而构造的CMOS A/D转换器。 它们设计成能通过3态数据输出和模拟输入与微处理器或外围设备串行接口。TLC549仅用输入/输出时钟(I/O CLOCK)和芯片选择 (CS)输入作数据控制。TLC549的IO CLOCK输入频率最高可达1.1MHz。

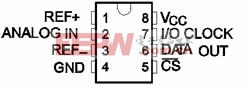

TLC549提供了片内系统时钟,它通常工作在4MHz且不需要外部元件。片内系统时钟使内部器件的操作独立于串行输入/输出的时序并允许TLC548和TLC549象许多软件和硬件所要求的 I/O CLOCK和内部系统时钟一起可以实现高速数据传送以及对于TLC549为每秒40,000次转换的转换速度。TLC549 的引脚排列分别如图3-17下。

如图3-17 TLC549 的引脚排列

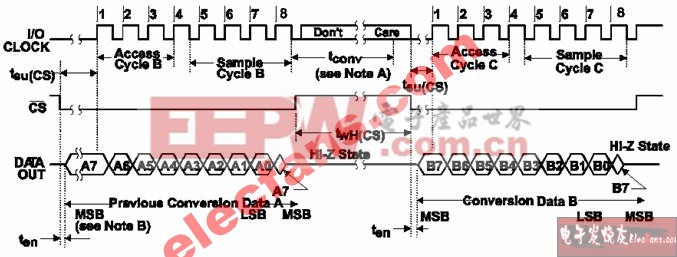

TLC549 的工作时序如图3-18所示。

图3-18 TLC549 的工作时序

转换周期需要36个系统时钟周期(最大为 17μs),它开始于CS变为低电平之后I/O CLOCK的第8个下降沿,这适用于该时刻其地址存在于存储器中的通道。

在CS变为低电平后,最高有效位 (A7)自动被放置在DATA OUT总线上。其余的7 位(A6-A0)在前7个I/O CLOCK下降沿由时钟同步输出。

TLC549的工作原理

TLC549是在单个芯片内的完善的数据采集系统。每一个器件包含内部系统时钟,采样和保持,8位A/D转换器,数据寄存器以及控制逻辑电路。为了提高灵活性和访问速度,器件有两个控制输入:I/OCLOCK和芯片选择(CS)。这些控制输入和与TTL兼容的3态输出易于与微处理器或小型计算机的串行通信。器件可在17μs或更短时间内完成转换。TLC549每25μs重复一次完整的输入-转换-输出(input-conversion-output)周期。

内部系统时钟和I/OCLOCK独立使用且不需要任何特定的速度或二者之间的相位关系。这种独立性简化了器件的硬件和软件控制任务。由于这种独立性和系统时钟的内部产生,控制硬件和软件只需关心利用I/O时钟读出先前转换结果和启动转换。内部系统时钟以这种方式驱动转换电路以便控制硬件和软件不需要涉及此项任务。

当CS为高电平时,DATAOUT处于高阻状态且I/OCLOCK(I/O时钟)被禁止。正常控制时序为:

1.CS被拉至低电平。当CS变为低电平时,前次转换结果的最高有效位(MSB)开始出现在DATAOUT端。

2.前4个I/OCLOCK周期的下降沿输出前次转换结果的第2、第3、第4和第5个最高有效位。在I/OCLOCK第4个高电平至低电平的跳变之后,片内采样和保持电路开始对模拟输入采样。采样操作主要包括内部电容器充电到模拟输入电压的电平。

3.其后再把三个I/OCLOCK周期加至I/OCLOCK端,在这些时钟周期的下降沿,第6、第7和第8个转换位被移出。

4.最后(第8个)时钟周期被加至I/OCLOCK。此时钟周期高电平至低电平的跳变使片内采样和保持电路开始保持功能。保持功能在接着四个内部系统时钟周期内继续进行,在此之后保持功能结束且在下面32个系统时钟周期内完成转换,总共为36个周期。在第8个I/OCLOCK周期之后,CS必须变为高电平,否则I/OCLOCK必须保持低电平达至少36个系统时钟周期以供保持和转换功能的完成。在多个转换周期内CS可保持低电平。在多个转换周期内使CS保持低电平时必须特别注意防止I/OCLOCK线上的噪声闪变。如果在I/OCLOCK上发生闪变,那么在微处理器/控制器和器件之间的I/O时序将失去同步。此外,如果CS变为高电平,那么它必须保持高电平直至转换结束为止。否则,CS的有效高电平至低电平跳变将引起复位,它使正在进行的转换失败。

在36个系统时钟周期发生之前,通过完成步骤1至4可以启动新的转换,同时正在进行的转换中止。此操作产生先前的转换结果而不是正在进行的转换结果。

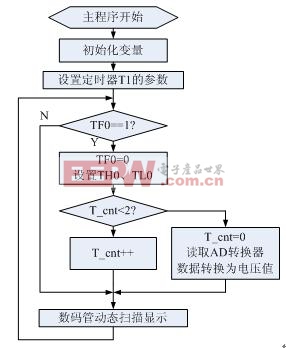

(3)分析软件任务要求,写出程序设计思路,分配单片机内部资源,画出程序流程图

软件的任务包括定时器的定时功能、AD转换器TLC549的控制与数据的读取,数码管的动态扫描。程序设计思路,采用查询定时器中断标志的方式来启动AD转换器TLC549的工作,在读取AD转换器的数据之后,再对数据进行计算换算为对应的电压值。

需要分配的单片机存储资源包括AD转换器数据的暂存变量(re_data)、定时器溢出次数的计数变量(T_cnt)、数据换算的系数(xishu)以及电压值(volt)等。

主程序的流程图如图3-19所示。由于采用查询中断标志的方式来响应的中断,所以主程序要循环完成如下任务:中断标志的查询、AD转换器数据的读取、电压值的换算以及数码管的动态扫描显示。

(4)设计系统软件调试方案、硬件调试方案及软硬件联合调试方案

软件调试方案:伟福软件中,在“文件新建文件”中,新建C语言源程序文件,编写相应的程序。在“文件新建项目”的菜单中,新建项目并将C语言源程序文件包括在项目文件中。

在 “项目编译”菜单中将C源文件编译,检查语法错误及逻辑错误。在编译成功后,产生以 “*.hex”和“*.bin” 后缀的目标文件。

硬件调试方案:在设计平台中,将单片机的P1.0接TLC549的CLK管脚,P1.1接TLC549的DOUT管脚,P1.2接TLC549的CS管脚。

在伟福中将程序文件编译成目标文件后,将下载线安装在实验平台上,运行“MCU下载程序”,选择相应的flash 数据文件,点击“编程”按钮,将程序文件下载到单片机的Flash中。

然后,上电重新启动单片机,检查所编写的程序是否达到题目的要求,是否全面完整地完成试题的内容。

3.6.2 模块2 程序设计

//晶振:11.0592MHz,定时器T0每50ms中断一次,每隔0.1秒读ADC一次

/* AD转换器使用 TLC549

DIY机械键盘相关社区:机械键盘DIY

评论