采用LPC2378和ADS112的视频矩阵切换装置设计

目前,国内使用的视频矩阵切换系统一般规模较小,并且大多数通过RS232串口连接的键盘来控制视频矩阵的切换,实施远程操控很繁琐。

本文引用地址:https://www.eepw.com.cn/article/171918.htm本文采用NXP公司基于ARM7的微控制器LPC2378与ADI公司的视频矩阵切换芯片ADS112构成了视频矩阵切换装置,实现了具有以太网接口的64路视频输入、8路视频输出的视频矩阵。监控中心可以通过网络传输的方式将视频切换控制命令和云台操作控制命令发送给LPC2378,再由LPC2378根据协议处理上位机发来的命令数据,控制视频矩阵和摄像机云台。这样,操作人员可以使用可视化的上位机,通过以太网对视频进行切换。在上位应用软件的支持下,该系统具有自动、循环切换视频的功能,并且可以通过网络通信的方式,在远端对各摄像机的云台实施操作。

1 LPC2378的特性

LPC2378包含了10/100M Ethernet MAC、USB 2.0全速接口、4个UART、2路CAN通道、1个SPI接口、2个同步串行端口(SSP)、3个I2C接口、1个I2S接口、MiniBus、4个通用定时器、10位A/D转换器、RTC、看门狗和104个通用I/O引脚。LPC2378的特性如下:

①ARM7TDMI-S处理器,可在高达72 MHz的工作频率下运行。

②高达512 KB的片内Flash程序存储器,具有在系统编程(ISP)和在应用编程(IAP)功能。单个Flash扇区或整个芯片擦除的时间为400 ms,256字节编程的时间为1 ms。Flash程序存储器在ARM局部总线上,可以进行高性能的CPU访问。

③ARM局部总线上有高达32 KB的SRAM,可以进行高性能的CPU访问。

④以太网接口的16 KB静态RAM,也可用作通用SRAM。

⑤USB接口的8 KB静态RAM,也可用作通用SRAM。

⑥2个AHB系统,可以同步进行Ethernet DMA、USB DMA以及从片内Flash执行程序的操作,这些功能不会产生竞争。总线桥允许Ethernet DMA访问其他AHB子系统。

⑦外部存储控制器支持诸如Flash和SRAM的静态设备,8位数据/16位地址并行的总线仅可在LPC2378中使用。

⑧先进的向量中断控制器,支持多达32个向量中断。

⑨通用AHB DMA控制器(GPDMA)能够与SSP串行接口、I2S端口和SD/MMC卡端口共用,也可用于存储器到存储器的传输。

LPC2378内部集成的Ethernet控制器使用RMII接口与外围电路PHY芯片(例如DM9161A)进行通信,从而易于实现以太网通信功能。

2 AD8112的功能特点

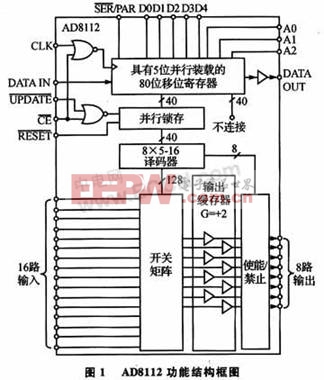

ADSll2是ADI公司的16路输入、8路输出的视频矩阵切换芯片,所有的输入和输出都具有缓存。ADS112具有由128个独立的电子开关构成的开关矩阵,可以实现16路视频输入、8路视频输出。该矩阵切换是100%非阻塞的,通过串行或并行编程方式写入控制系列字,可以使能任意一路输入和任意一路输出连接,每一个输出可以和16拟输入信号中的任意一路连接。AD8112功能结构框图如图1所示。

AD8112的输出端设有高速放大器,放大器的补偿是自动地优化到每一个增益选择的最大带宽。每一个输出可以由控制系列字的第5位控制使能。当被禁止时,输出引脚可以视为一个4 kΩ的电阻,并且允许将多个禁用的输出引脚连接在一起。当上电或者异步复位时,所有的输出引脚将被初始化成禁止状态,避免在大规模视频矩阵中的输出发生冲突。

AD8112的数字接口由以下引脚组成:DATA IN,DATAOUT,CLK,LIPDATE,CE,SER/PAR,194~D0,A2~A0和RESET。其中,DATA IN是串行数据输入端,DATA OUT是串行数据输出端,CLK是串行输入时钟,UPDATE是数据锁存端,CE是片选端,SER/PAR是编程方式控制端,D4~D0和A2~A0是并行数据和地址装载端,RESET是复位端。

AD8112提供串行编程和并行编程2种编程方式,由SER/PAR引脚的高低电平进行选择。SER/PAR=0时,选择串行编程方式:DATA IN输入的数据在CLK的下降沿进行装载,在UPDATE的下降沿锁存数据,对矩阵进行编程;DATA OUT经80位矩阵模式寄存器移位输出。SER/PAR=1时,选择并行编程方式:由D4~D0并行输入的数据和A2~A0并行输入的地址在CLK的下降沿进行装载;在UPDATE的下降沿锁存数据,对矩阵进行编程。

AD8112串行编程方式控制时序图如图2所示。

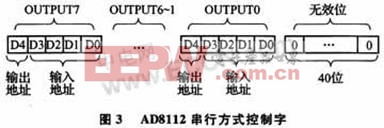

在串行编程方式下,AD8112从DATA IN端输入的控制字如图3所示。控制字前40位每5位对应一个视频输出,按OUTPUT7~OUTPUT0依次排列。D4控制输出使能,D4=1输出使能,D4=0输出禁止;D3~D0选定视频输入端INPUT15~INPUT0。由于AD8112内带的5位并行装载的80位移位寄存器中,有40位在内部不连接,故控制字的后40位写入0。

对于一个由N块AD8112组成的大型矩阵,这些芯片可以被一串N×80位的串行数据流编程。AD8112并行编程方式控制时序图如图4所示。

评论