嵌入式大屏幕LED显示屏的设计与实现

摘 要:鉴于传统的LED显示规模小、可靠性差、需要上位机实时控制的问题,提出一种基于FPGA和2片SRAM的嵌入式大屏幕LED显示的方法,其显示规模达到512×512点阵列,并且可以在完全不需要上位机控制的情况下实时独立的工作。本设计已经实际使用在现场厂房中,能够较好地对厂房中的生产情况进行实时显示。着重讨论该系统最底层的硬件连接及相应的软件设计,并给出其软、硬件实现。

本文引用地址:https://www.eepw.com.cn/article/168583.htm1 引 言

LED显示屏的应用已经比较普遍,而且随着应用的普及,更多新式的LED显示屏会应用在更多的场合,所以研究嵌入式大屏幕点阵LED的显示很有实际意义。

但是现在市场上的多种LED显示屏在显示性能上良莠不齐,并且大多需要上位机对显示过程进行实时控制。本文提出一种优化的高性能高可靠性的嵌入式大屏幕LED显示系统,只需要用1片FPGA和2片SRAM就可以实现大屏幕LED显示的驱动和内容更换,可以说其性能已经大有改善。本设计可以应对多种大屏幕显示的场合。

2 系统硬件设计与实现

硬件连接的方式多种并且灵活,其连接方式直接影响到显示的性能。下面给出的硬件连接方式是最优的方式,能够达到高性能的显示,并且使软件编写变得简单。

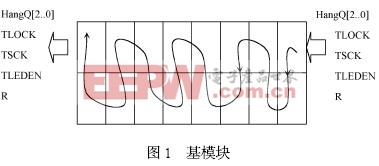

每个8×8的LED点阵块称为最小模块。每16个8×8的LED点阵块为一个基模块,一个基模块横向有8个,纵向有2个最小模块,如图1所示。图中每个小方格代表一个最小模块。

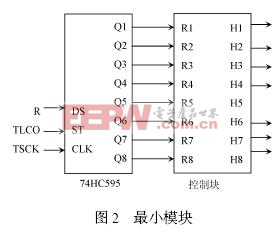

每个最小模块控制信号为8个行信号H1~H8和8个数据信号R1~R8。行信号接一个38译码器74HC138的输出,他的输入为HangQ[2..0];而列信号给具体这一行的数据信号接的是一个74HC595的输出,如图2所示。

在上半屏显示中,又将其分为8个512×32的块,这样的块叫单独显示模块,也就是说将横向的2行基模块看成一个单独的模块并用单独的一组信号进行控制,上半屏就要8组信号控制。这8组信号除了数据信号R不同外,其他的信号都是一样的。也就是说,在上半屏显示中8条数据线同时给上半屏的8个单独显示模块串打数据,当然只是给单独显示模块中的最小模块的某一行打满数据,然后再给下半屏打入数据。所以下半屏的情况与上半屏基本一样,除了8组数据信号R不同外,还有时钟信号也不一样。输入数据时,上半屏的时钟信号首先有效,根据基模块的理论要输入2048个脉冲以后上半屏的数据才被灌满;然后下半屏的数据才有效,从而输入下半屏的数据,情况与上半屏完全一样。

在扫描显示中,首先上半屏的8组控制信号的时钟脉冲信号有效,并且在这个过程中,8组控制信号的数据信号R有效,所以就可以先将上半屏的8个单独显示模块中的最小模块的某一行灌满数据。然后用同样的方法将下半屏的8个单独显示模块中的最小模块的某一行灌满数据,当然上半屏和下半屏灌满的都是最小模块的相同的一行。最后数据锁存信号和行锁存信号有效,使其显示。在这个过程中要注意的是数据信号R,因为要显示整屏的数据,在软件编写的过程中要将某个位置显示的数据准确的显示在该位置,就要从内存中准确的取出这个数据。

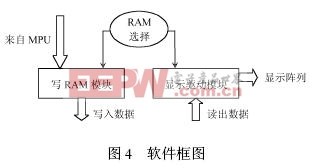

每一帧显示的数据大小为32768B,对于2块RAM交替工作的情况是完全符合要求的。并且SRAM的存取速度快,换帧的时候也能够很好地显示出预期的数据。程序中用一个RAM选择模块,用来选择某个时间是读出哪一块RAM,还是写入哪一块RAM。

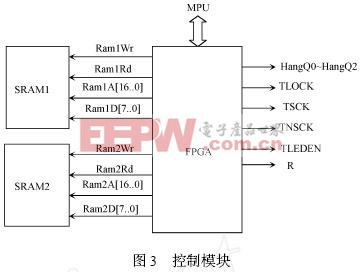

FPGA与存储器联接的信号为am1A[16..0], Ram1D[7..0], Ram1Rd, Ram1 Wr; Ram2A[16..0], Ram2D[7..0], Ram2Rd, Ram2Wr。当FPGA从Ram1取出数据进行显示时,其中有关Ram1的信号就有效;同时就给Ram2写数据。程序中还用到4个内部变量Rt[7..0][7..0],Gt[7..0][7..0],Rs[7..0][7..0]和Gs[7..0][7..0]分别代表4个数组,每个数组里有8个字节。

程序中用到1个全局时钟clk,他用来驱动1个内部全局信号counter_temp,他是1个15位的矢量。TSCK和TNsck信号将8个clk时钟周期作为他们的1个时钟周期,也就是说8个clk时间送出1位数据。FPGA读RAM的时序为:首先地址信号出现在RamxA[16..0]上,然后RamxRd,RamxWr分别置为低电平和高电平,经过12~15ns,读出的数据就会出现在RamxD[7..0]上以便FPGA读这个数来显示。

FPGA写Ram的时序是外部MPU信号控制,首先地址信号出现在Ram2A[16..0]上,然后RamRd, RamWr分别置为高电平和低电平,写的数据出现在Ram2D[7..0]上。经过很短的时间,数据就写入了。

程序设定FPGA中的Ram1D和Ram2D为双向口,可写可读。在内部要设相应的缓冲器。因为写RAM是MPU写给RAM,MPU要指明写的地址和数据,所以在程序中要有地址和数据输入口。实际设计中为了减少FP2GA的端口,设计成低地址和数据复用线AD[7..0],用一个信号ALE选择;当其为低电平时,AD[7..0]有效的数据是地址,为高电平时为要写入RAM中的数据。

静态图像显示过程中为了使眼睛看上去不闪烁,就要使一帧图像在一秒内至少显示50次,即使一帧图像在最多20ms显示完。要达到这个要求,就要使一个最小模块的8行在最多20ms内完成一个循环显示。因为是上半屏与下半屏分开传输数据,所以要求在最多1.25ms内传完半屏数据,时钟周期需要在0.6μs以下,而选用的FPGA的时钟频率可以达到50MHz以上,完全符合显示的要求。

4 结 语

硬件连接和软件设计是融为一体的,在最初系统的整体规划中,就是要兼顾两者。本设计从硬件连接到最后的软件实现,都是优化以后的结果。所以按照本设计中的硬件连接情况而设计的软件,只需要一片2万门的FPGA就可以实现如此大规模的点阵显示,并且本设计的LED显示屏,画面非常清晰稳定,并且在换帧的过程中能够做到流畅自如,看不出停滞。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论