智能型SRIO交换器增强基站预处理功能

——

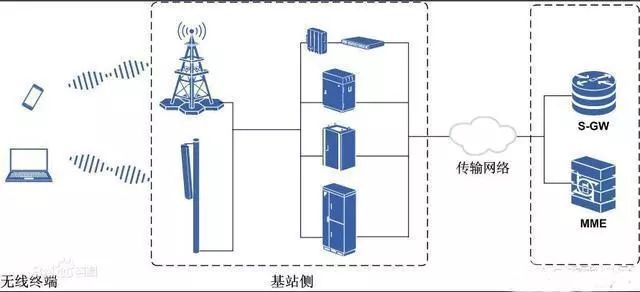

但是,到哪里才能找到有用的功能呢?IDT的解决方案是检查与交换核心相连的DSP芯片以及芯片速率硬件正在操控的处理任务,并了解一下在发送和接收操作期间是否存在某些简单、经常出现的任务。就像您或许已从本文的标题所预料到的那样,答案是“存在”。样本内数据操作(比如符号扩充和字节存储次序转换)以及多信息包操作(比如组播、样本重新排序和样本求和)中都有,有些存在于高速码片率处理硬件中,而有些则存在于DSP芯片上的符号率处理中。由于这些操作是比较标准的,不会随着时间或者上下文而发生变化,并且以某种频度出现,IDT公司便把它们从码片率和符号率硬件上卸载下来,并将其转移到交换芯片内部的专用硬件中。

据IDT公司的资深产品经理Bill Beane称,当您向基站设计团队介绍这种情形时,硬件设计师通常的反应是:“这很好,请把集合数据速率向我复述一遍。”然而,软件小组的负责人则会立即对卸载能力表示出兴趣。如果他们能够把任何重复的例行任务从DSP代码中卸载掉,则意味着硬件将会拥有更大的代码空间和更多的执行时间。

所以,IDT公司今天宣布的就是这样一款SRIO交换芯片(见图)。该芯片支持40个SRIO链接,每个端口的速度高达3.125Gbps。这些链接可被分为4个一组,并可通过配置驱动器来支持芯片至芯片或背板SRIO互连。该芯片还支持SRIO标准优先级和排队算法,以管理有可能变得复杂的多芯片对话中的数据流。另外,此芯片还支持该标准的误差管理和维护功能。

对高性能、小尺寸芯片和易管理功率的竞争需求限定交换核心必需采用一种网状配置。顺便说一下,功耗是设计中的一个重要问题,不是因为它过大,而是因为它与使用状况密切相关。Beane说,设计工作的相当一部分内容是模拟各种处理拓扑结构和算法,并一一检验它们的数据流和功耗。

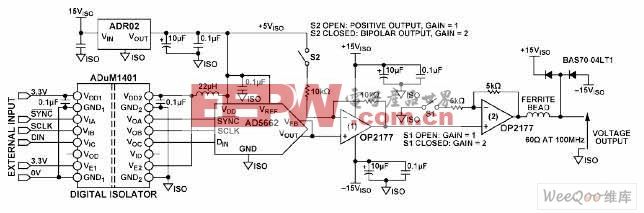

被卸载的处理任务出现在一个与位于输入和输出判优器组之间的交换核心并列的块中。该块包括10个相同的寄存器编程状态机;输入和输出缓冲器位于这些状态机的周围。每个状态机都能够执行样本内、多样本和求和操作,而且,全部10个状态机可以并行工作。

最终的结果是实现了典型基站处理系统中任务的重新分配。不管是其本身还是对于包处理软件小组而言,该任务都不是无足轻重的。因此,IDT公司将在7月份提供一款高级夹层卡(Advanced Mezzanine Card)外形的参考设计方案,该设计将包括一块带有4个德州仪器Himalaya DSP的完整、可满足生产要求的评估板和一个延迟准确的仿真器。IDT 70K2000Z现在可以提供样片,并将于11月投产。价格约125美元(以10 000片为批量时)。

评论