基于ADV212的高清视频压缩系统设计

1 ADV212的编解码原理

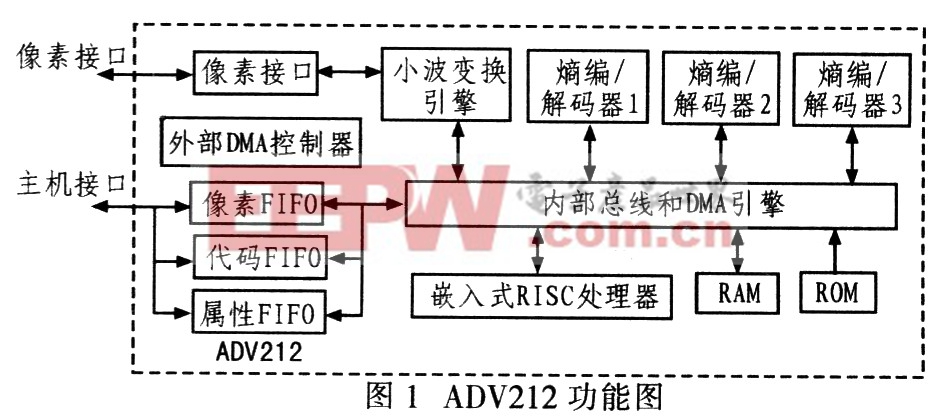

图l所示为ADV212的功能图,主要由像素接口、小波变换引擎、熵编/解码器、嵌入式RISC处理器、存储器系统和内外部DMA等组成。操作的基本流程是视频或像素数据通过ADV212像素接口输入,有效采样值则经过隔行扫描传输到小波变换引擎中(小波变换引擎,可以对码块进行高达6级的小波分解)。进入小波变换引擎的数据被分瓦片或帧,每个瓦片或帧将通过5/3定点运算或9/7浮点运算滤波器分解成许多子带,并生成相对应的小波系数,然后写入内部寄存器中。3个熵编/解码器用来对小波系数的编码块进行背景建模和算术编码,并在压缩过程中计算最佳速率和失真度。熵编码形成的JPEG2000标准的数据码流被存入代码FIFO中。代码FIFO主要缓冲内部高速总线和低速主机接口。码流数据可通过共用的读写存取协议(

2 统硬件设计

本方案作为实现高清视频数据压缩系统,首先从系统实现功能和性价比上考虑,采用FPGA+ADV212来实现。

视频解码器选取:视频解码器选用ADV7402型高清视频解码器。它采用10位ADC,12个模拟输入,支持标清(480i,NTSC,PAL,SECAM)、高清(1080i,720p)和图形RGB输入(1 280xl 024@60 Hz),可以实现与ADV212无缝连接。

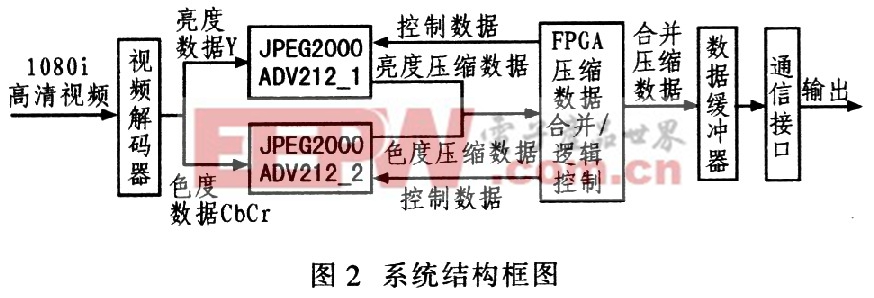

ADV212片数选取:1个10 bit的高清晰度(HDTV)视频信号,输入数据传输率大约为124 Ms/s,而ADV212像素接口输入速率限制,在不可逆模式下为65 MS/s,可逆模式下为32 MS/s。这就要求系统至少要由2片ADV212组成,本系统选择2片ADV212压缩器件,YCbCr数据采取在4:2:2格式,分别完成亮度(Y)和色度(CbCr)的数据压缩处理,输入数据使用是EAV/SAV编码格式。图2所示为系统结构框图,本方案包括视频采集解码模块、视频图像JEPG200压缩模块、压缩合并模块、逻辑控制模块和通信输出模块。

FPGA选取:选用Altera公司的CycloneIII系列EP3C55F484C8器件,其具有328个用户I/O,55 856个可用逻辑元,312个嵌入式乘法器单元和4个锁相环,可轻松实现ADV212初始化及压缩数据捕获和亮度压缩数据与色度压缩数据的合并等功能。

3 ADV212器件初始化流程和参数配置

3.1 ADV212初始化流程

ADV212初始化程序依据特定的指令命令配置ADV212内部直接寄存器和间接寄存器来完成。图3所示为ADV212编码初始化流程,初始化程序从PLL寄存器、BOOT寄存器、MMODE寄存器和BUSMODE寄存器等直接寄存器的接入开始,访问直接寄存器时目标系统必须保持输入管脚ADDR,![]() ,和HDATA(写)的状态。当装载完固件和配置参数后,软件重启,然后再次配置BUSMODE和MMODE寄存器和应用特殊寄存器。下一步,要确定正确的固件被应用ID装载。正确的固件装载能被EIRQFLG寄存器的中断或投票程序证实。当你确定固件连接装载和EIRQFLG寄存器清零后。编码开始。

,和HDATA(写)的状态。当装载完固件和配置参数后,软件重启,然后再次配置BUSMODE和MMODE寄存器和应用特殊寄存器。下一步,要确定正确的固件被应用ID装载。正确的固件装载能被EIRQFLG寄存器的中断或投票程序证实。当你确定固件连接装载和EIRQFLG寄存器清零后。编码开始。

3.2 ADV212参数配置

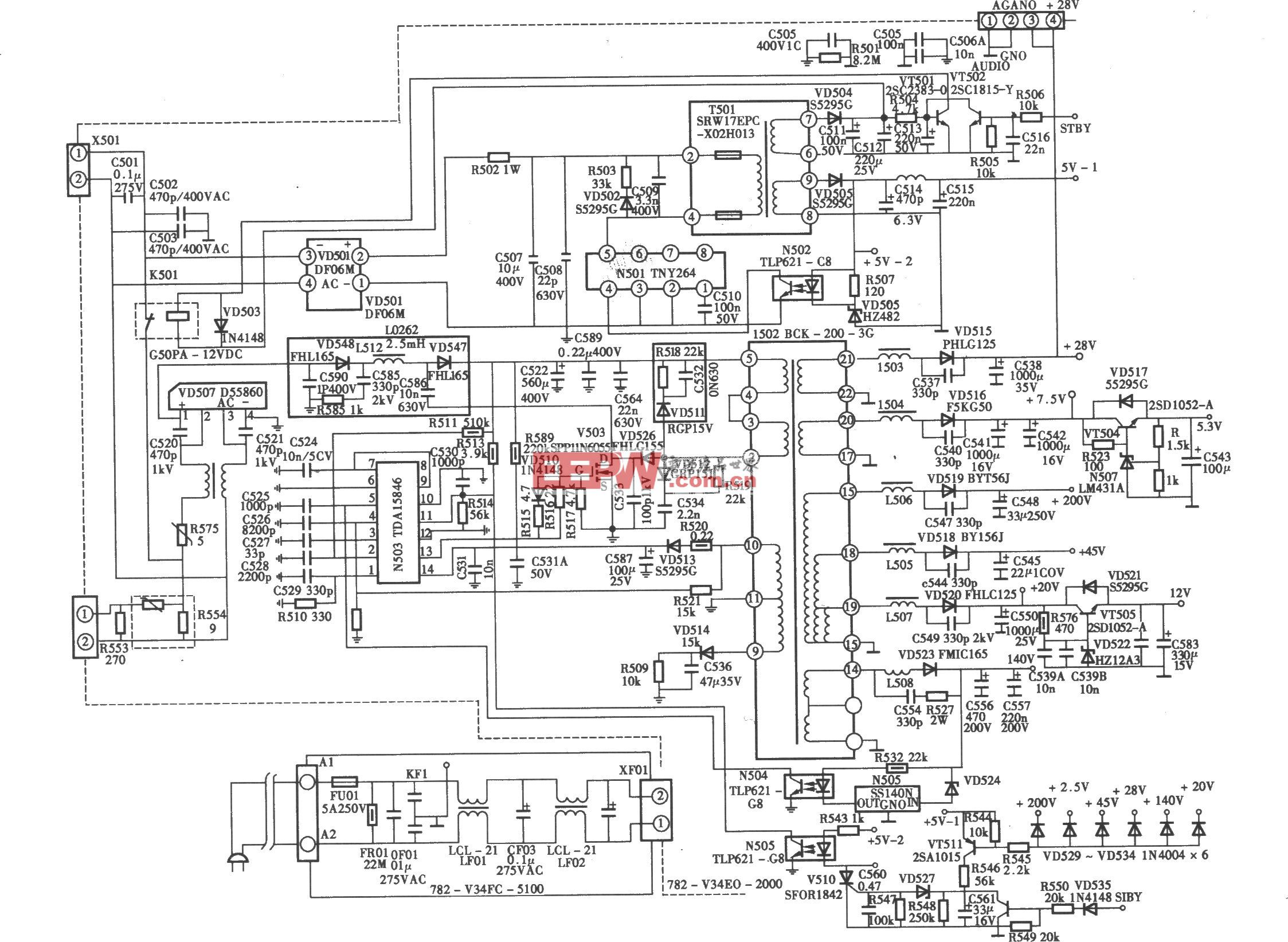

时钟配置:高清视频1080i要求VCLK为74.25 MHz。根据ADV212的数据表,JCLK必须至少为2VCLK,因此最大的脉冲频率推荐为0.35J-CLK,这接近50 MHz,这是最大的读写脉冲频率。

总线及DMA配置:HDTV(1080i)应用时,2个ADV212必须工作在不可逆最大传输率为65 MS/s模式,视频输入采取32位VDATA总线(像素接口),压缩数据输出采取2个ADV212共享32位HDATA总线(主机接口)。初始化ADV212选择属性类型5(ATTRTYPE),属性数据读取采用单一传输的DREQ/DACK DMA模式,码流读取采取脉冲传输DREQ/DACK DMA模式。

评论